武夷学院实验报告课程名称:逻辑设计与 FPGA 项目名称: 乐曲硬件演奏电路设计 姓名: 专业:微电子学 班级: 14 微电子 学号: 04 实验日期 音符的持续时间需根据乐曲的速度及每个音符的节拍数来确定,TONETABA 模块的功能首先是为 SPEAKERA 提供决定所发音符的分频预置数,而此数在 SPEAKERA 输入口停留的时间即为此音符的节拍值

TONETABA 模块是乐曲简谱码对应的分频预置数查表电路,其中需设置“梁祝”乐曲全部音符所对应的分频预置数,共 13 个,每一音符的停留时间由音乐节拍和音调发生器模块 NOTATABS 的 CLK 的输入频率决定,在此为 4HZ

这 13 个值的输出由对应于 TONETABA的 4 位输入值 INDEX[3

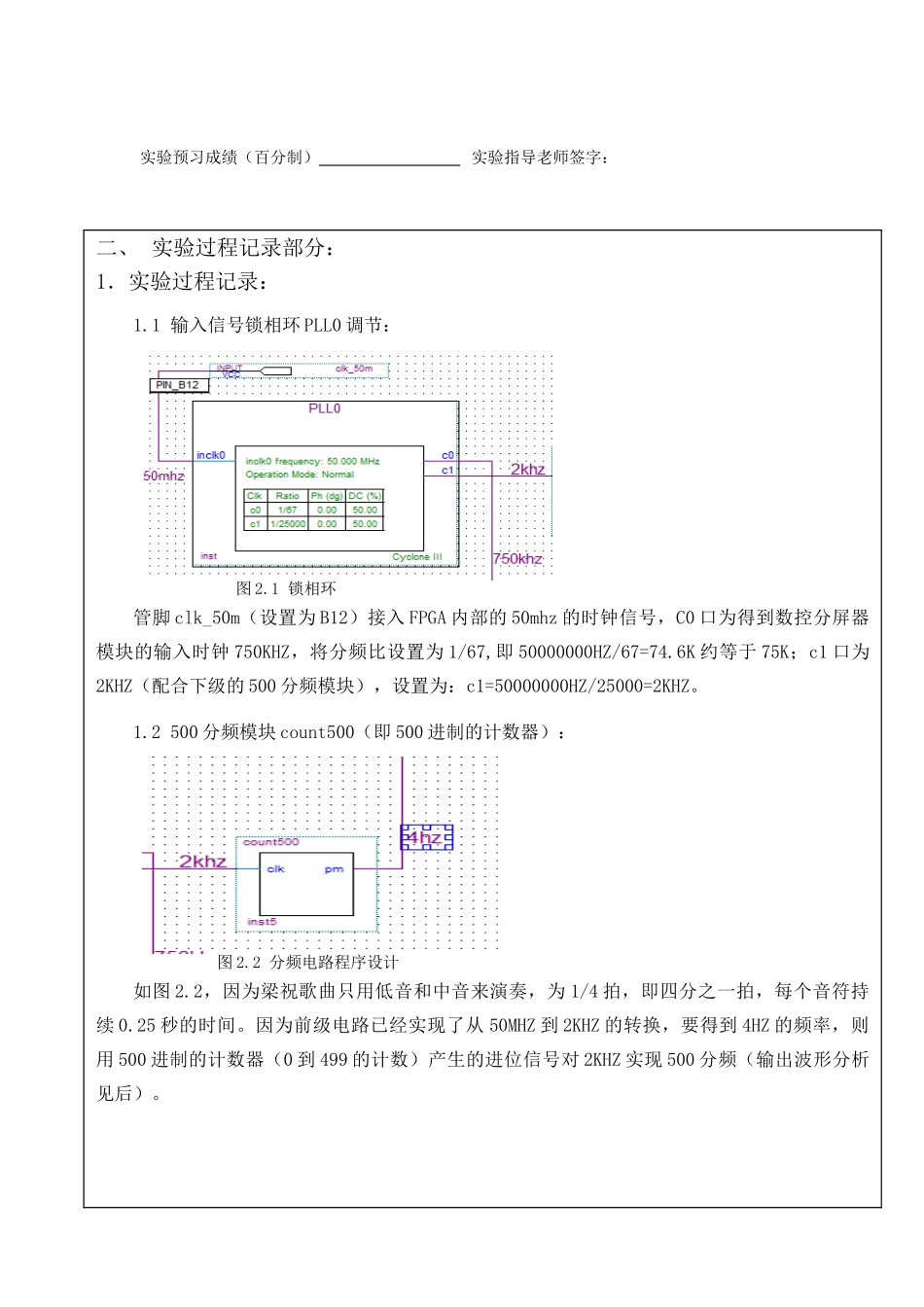

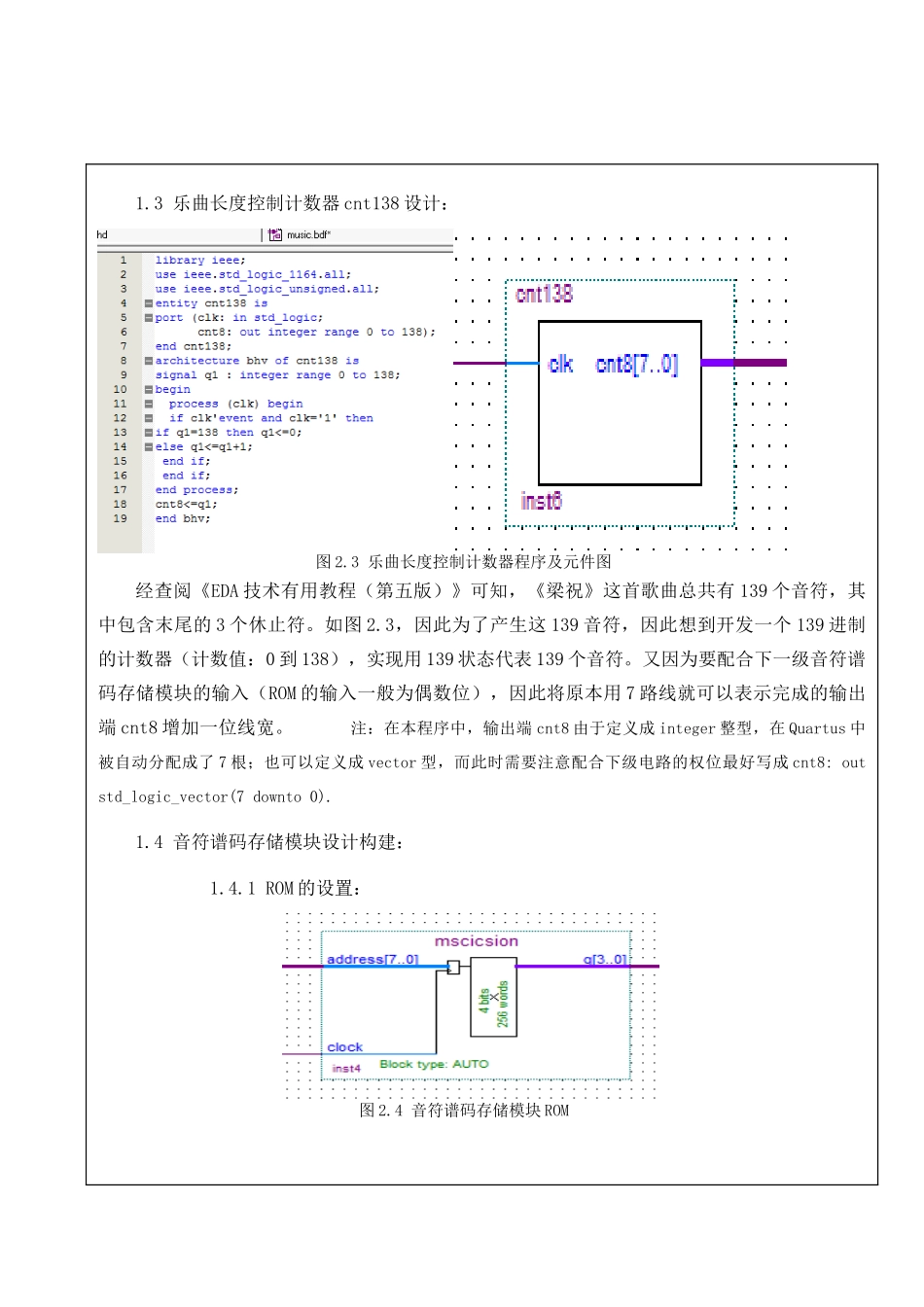

在 NOTETABS 中设置了一个 8 位二进制计数器(计数最大值为 138),作为音符数据 ROM 的地址发生器

这个计数器的计数频率选为 4HZ,即每一计数值的停留时间为 0

25 秒,恰为当全音符设为 1 秒时,四四拍的 4 分音符持续时间

例如,“梁祝”乐曲的第一个音符为“3”,此音在逻辑中停留了 4 个时钟节拍,即 1 秒时间,相应地,所对应的“3”音符分频预置值为 1036,在 SPEAKERA 的输入端停留了 1 秒

随着 NOTETABS 中的计数器按 4HZ 的时钟频率作加法计数时,即随地址递增时,音符数据 ROM 中的音符数据将从 ROM 通过 TONEINDEX[3

0]端口输向 TONETABA 模块,乐曲就开始连续自然地演奏起来了

具体参考教材实验 9-1 中说明

3.实验仪器:PC 机 1 台 QuartusII 系统开发板 1 块 开发板外接扬声器4.实验步骤及方法:分模块设计和仿真测试,通过后联合仿真测试,最后下载到硬件中测试

5.注意事项:所有实验数据放入一个文件夹内,