PCI-E布线规则合理的走线设计可以信号的兼容性,减小信号的反射和电磁损耗

PCI-E总线的信号线采用高速串行差分通信信号,因此,注重高速差分信号对的走线设计要求和规范,确保PCI-E总线能进行正常通信

PCI-E是一种双单工连接的点对点串行差分低电压互联

每个通道有两对差分信号:传输对Txp/Txn,接收对Rxp/Rxn

该信号工作在2

5GHz并带有嵌入式时钟

嵌入式时钟通过消除不同差分对的长度匹配简化了布线规则

随着PCI-E串行总线传输速率的不断增加,降低互连损耗和抖动预算的设计变得格外重要

在整个PCI-E背板的设计中,走线的难度主要存在于PCI-E的这些差分对

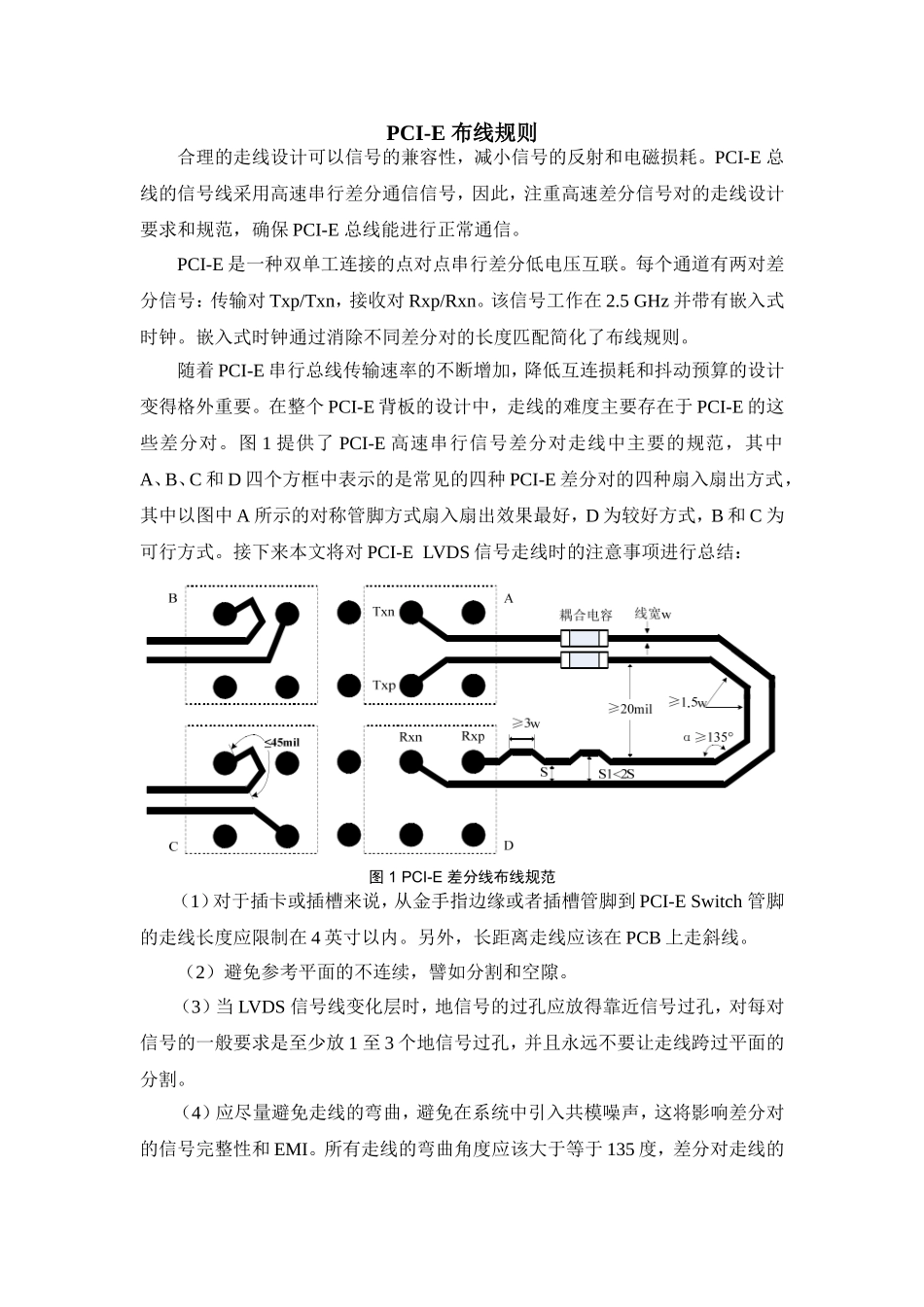

图1提供了PCI-E高速串行信号差分对走线中主要的规范,其中A、B、C和D四个方框中表示的是常见的四种PCI-E差分对的四种扇入扇出方式,其中以图中A所示的对称管脚方式扇入扇出效果最好,D为较好方式,B和C为可行方式

接下来本文将对PCI-ELVDS信号走线时的注意事项进行总结:图1PCI-E差分线布线规范(1)对于插卡或插槽来说,从金手指边缘或者插槽管脚到PCI-ESwitch管脚的走线长度应限制在4英寸以内

另外,长距离走线应该在PCB上走斜线

(2)避免参考平面的不连续,譬如分割和空隙

(3)当LVDS信号线变化层时,地信号的过孔应放得靠近信号过孔,对每对信号的一般要求是至少放1至3个地信号过孔,并且永远不要让走线跨过平面的分割

(4)应尽量避免走线的弯曲,避免在系统中引入共模噪声,这将影响差分对的信号完整性和EMI

所有走线的弯曲角度应该大于等于135度,差分对走线的间距保持20mil以上,弯曲带来的走线最短应该大于1

5倍走线的宽度

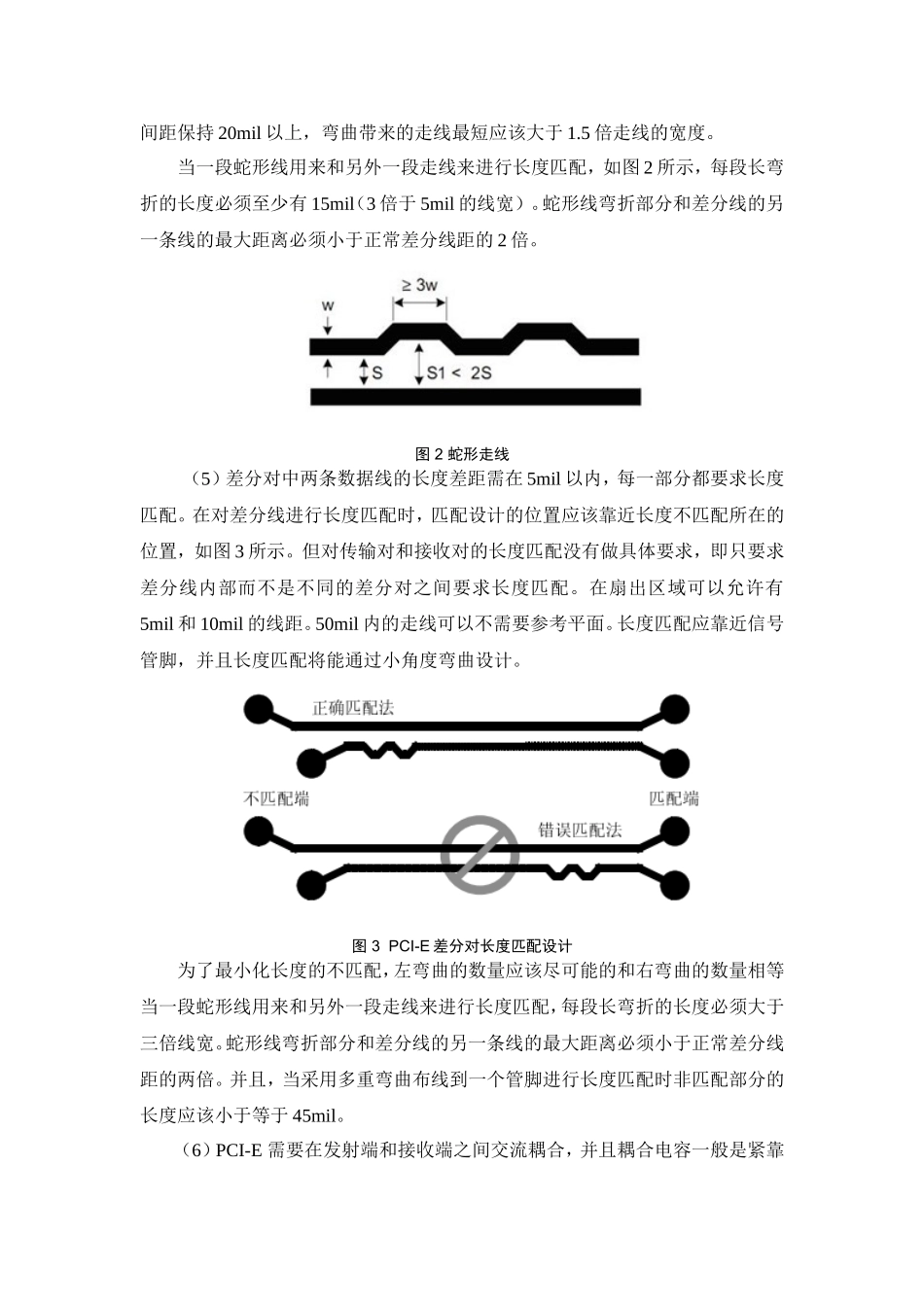

当一段蛇形线用来和另外一段走线来进行长度匹配,如图2所示,每段长弯折的长度必须至少有15mil(3倍于5mil的线宽)

蛇形线弯折部分和差分线的另一条线的最大距离必