16*16 点阵显示实验报告 1 16*16 点阵显示实验报告 一、实验目的 (1)学习点阵显示字符的基本原理

(2)掌握用数控分频控制速度,实现点阵扫描的基本方式

(3)会使用Quartus II 软件中的Verilog HDL 语言实现点真的行列循环显示

二、实验设备与器件 Quartus II 软件、EP2C8Q208C8 实验箱 三、实验方案设计 1

实验可实现的功能 可通过编写 Verilog HDL 语言,实现点阵的行列交替扫描

先是行扫描,扫描间隔为 1s,16 行都扫描完之后开始列扫描,扫描间隔仍然为 1s,16 列扫描完之后,行继续扫描,依次循环

点阵基本知识 16*16 扫描LED 点阵只要其对应的X、Y 轴顺向偏压,即可使LED 发亮

例如如果想使左上角 LED 点亮,则 Y0=1,X0=0 即可

应用时限流电阻可以放在 X 轴或 Y 轴

它有 16 个共阴极输出端口,每个共阴极对应有 16 个 LED 显示灯

LED 点阵每个点都有一个红色的发光二极管

点阵内的二极管间的连接都是行共阳,列共阴

本实验采用共阴,当二极管的共阳极为高电平,共阴极为低电平时,所接点发光;反之处于截止状态,不放光

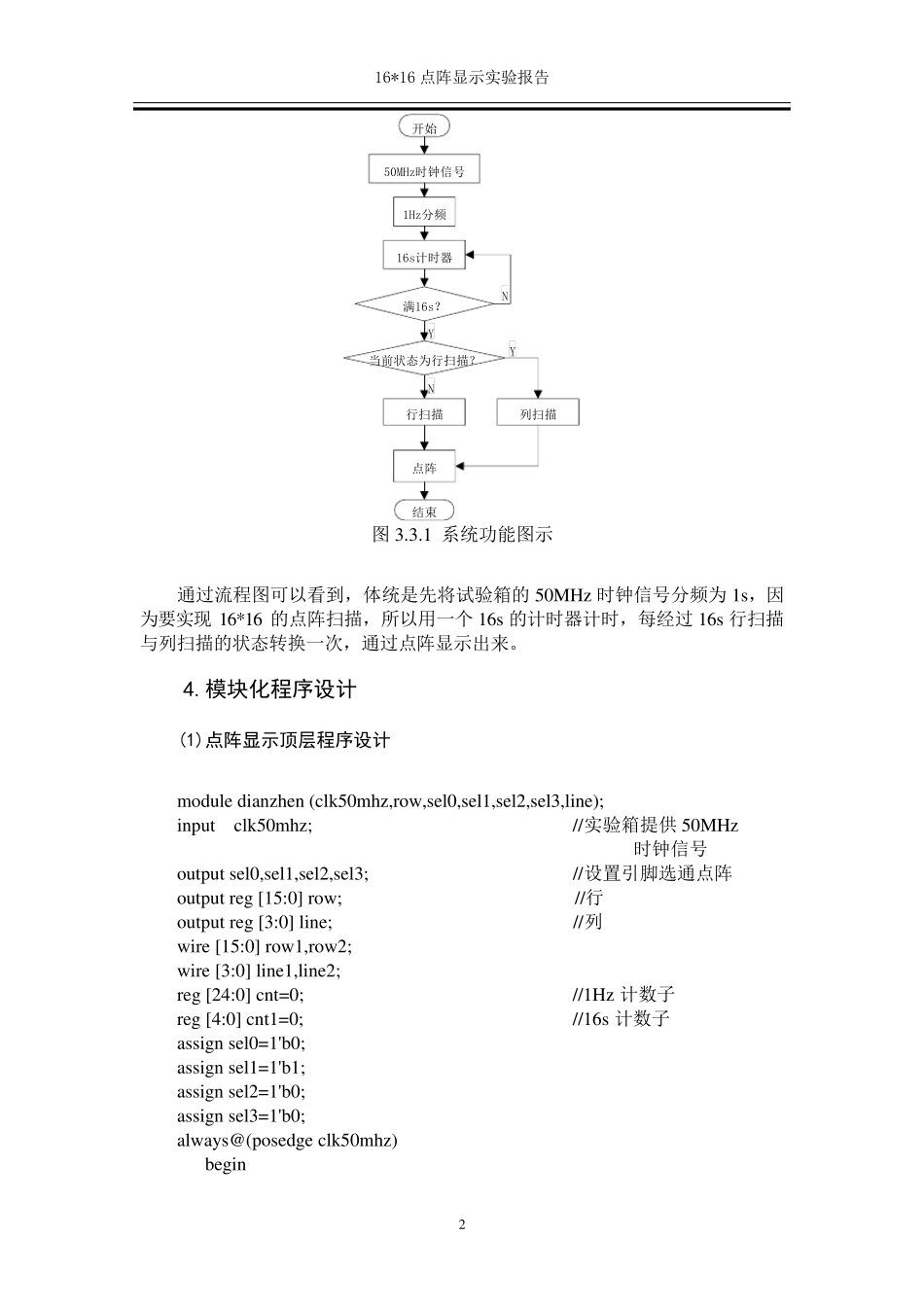

系统工作原理 本系统用了两个模块,其中dianzhen

v 是顶层文件,而 hangsaomiao

v 和liesaomiao

v是两个子模块,总体的系统功能框图如图3

16*16 点阵显示实验报告 2 50MHz时钟信号1Hz分频16s计时器开始满16s

当前状态为行扫描

NY行扫描列扫描NY点阵结束 图3

1 系统功能图示 通过流程图可以看到,体统是先将试验箱的50MHz 时钟信号分频为1s,因为要实现16*16 的点阵扫描,所以用一个16s 的计时器计时,每经过16s 行扫描与列扫描的状态转换一次,通过点阵显示出来