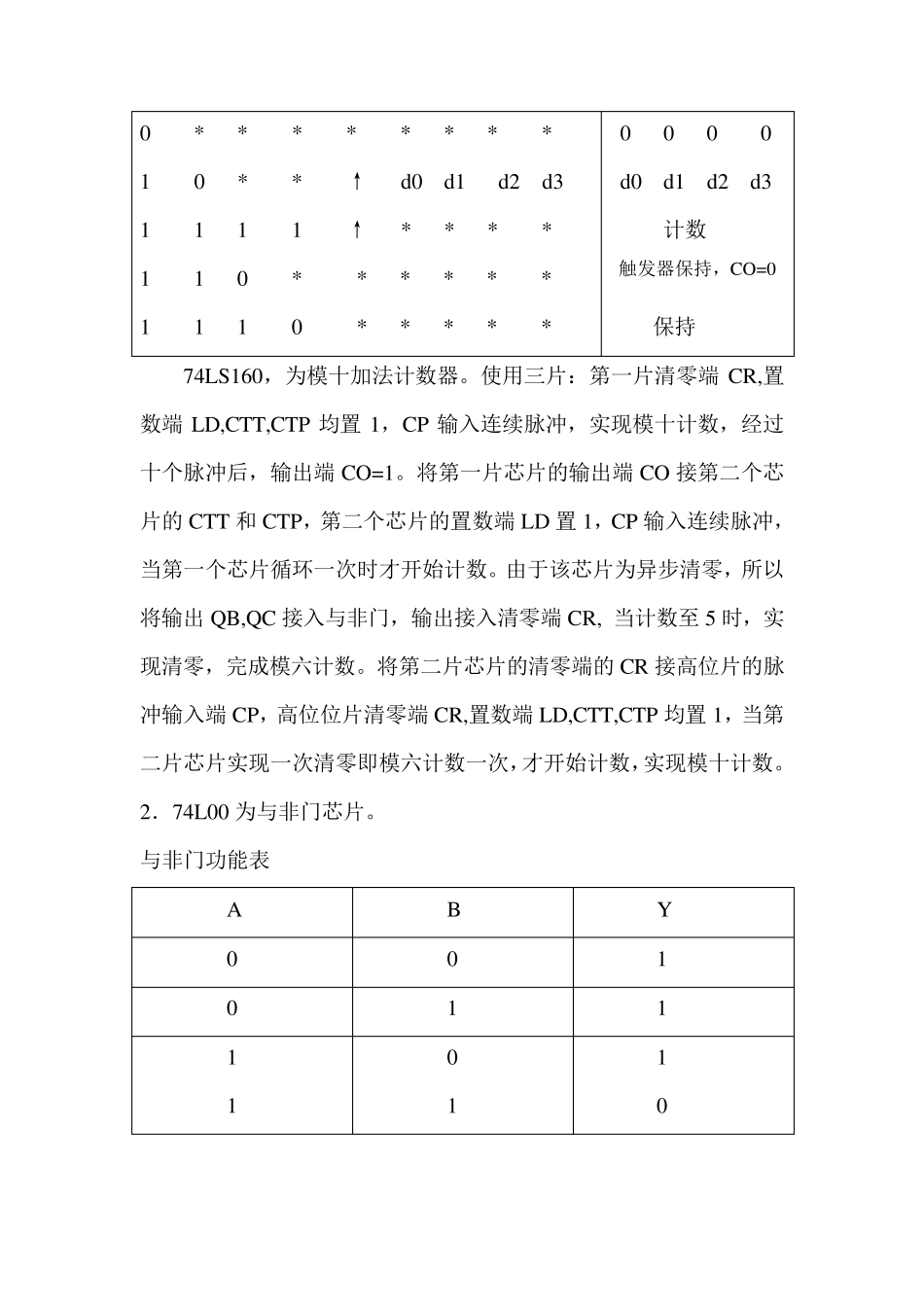

数字电路逻辑设计 课 程 设 计 专业班级:通信 08-01 姓名 : 学号 : 三位数字显示计时系统 一.设计要求 设计一个3 位数字显示的时间计数系统,以供运动员比赛用。要求精度到秒,最大计时9 分59 秒。可以用按钮开关控制计数器的启动,停止及清零,开机时可以自动清零。 二.设计方案 数字显示计时系统是通过控制电路使加法计数器对连续脉冲进行计数,而加法计数器通过译码器来显示它记忆的脉冲周期个数。 1. 连续脉冲发生: 可选用555 定时器构成的多谐振荡器产生,也可选用石英晶体振荡器,通过计数器分频产生,获得精确的秒脉冲信号。 2. 计数及译码显示: 加法计数器构成电子秒表的计数单元。分频器输出端取得周期为一秒的矩形脉冲送入计数器中。 三个计数器的输出端分别与三个数码显示译码器的相应输入端连接。可显示0:00——9:59 计时。 三.设计原理 1.74LS160 功能表; 输入 输出 CR LD CTT CTP CP D0 D1 D2 D3 Q0 Q1 Q2 Q3 0 * * * * * * * * 1 0 * * ↑ d0 d1 d2 d3 1 1 1 1 ↑ * * * * 1 1 0 * * * * * * 1 1 1 0 * * * * * 0 0 0 0 d0 d1 d2 d3 计数 触发器保持,CO=0 保持 74LS160,为模十加法计数器。使用三片:第一片清零端 CR,置数端 LD,CTT,CTP 均置 1,CP 输入连续脉冲,实现模十计数,经过十个脉冲后,输出端 CO=1。将第一片芯片的输出端 CO 接第二个芯片的 CTT 和 CTP,第二个芯片的置数端 LD 置 1,CP 输入连续脉冲,当第一个芯片循环一次时才开始计数。由于该芯片为异步清零,所以将输出 QB,QC 接入与非门,输出接入清零端 CR, 当计数至 5 时,实现清零,完成模六计数。将第二片芯片的清零端的 CR 接高位片的脉冲输入端 CP,高位位片清零端 CR,置数端 LD,CTT,CTP 均置 1,当第二片芯片实现一次清零即模六计数一次,才开始计数,实现模十计数。 2.74L00 为与非门芯片。 与非门功能表 A B Y 0 0 1 0 1 1 1 1 0 1 1 0 四.设计仿真(EW B 仿真) 五.设计实验操作 1.取实验所需芯片:一片74LS00,三片74LS160 2. 分别将三个74LS160 电源, 接地端接好,CP 接连续脉冲,ENT,ENP,LD,CLR 接1,QA,QB,QC,QD 接数码显示管的A,B,C,D,测试芯片的计数功能。74LS00 电源,接地接好,按与非门的功能表测试芯片功能。 3.测试完成后,按如上仿真电路图连线。 六.设计结果显示 0:00 0:01 0:02 … 0:09 0:10 … 0:19 0:20 … … 0:59 1:00 … … 9:59 0:00 七.设计总结及体会 通过实验我了解了 74LS106 同步加法计数器的各项逻辑功能,使低位片在循环一模十计数后,第二片开始计数,模六计数后清零且高位片开始计数,实现模十计数。最终得到从 0 :0 0 到 9 :5 9 的秒表计时系统。