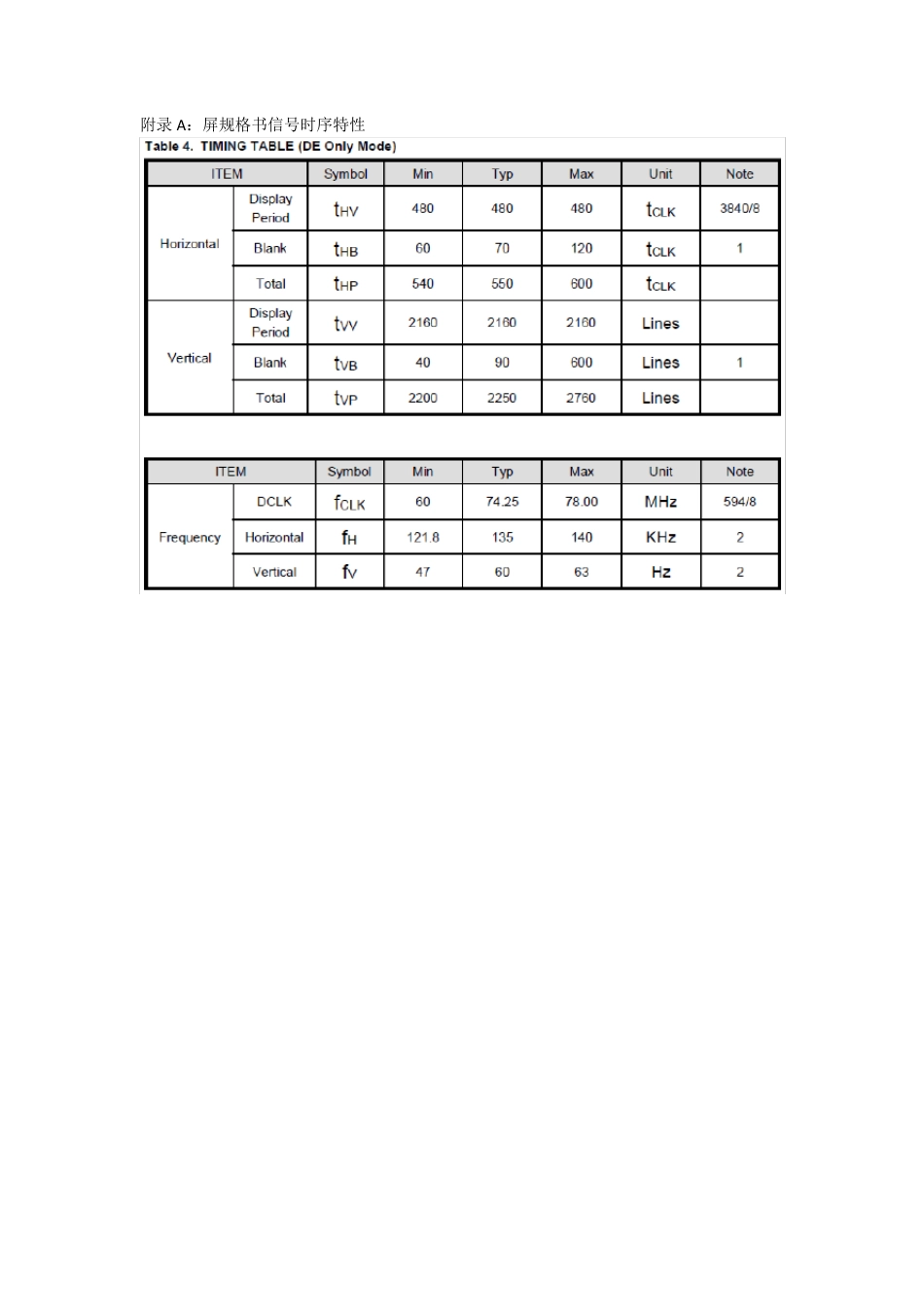

V-by-One 接口信号驱动原理(3840*2160) 一、时钟与像素点关系 一场:60Hz-16

667ms,2250 行(2160 行有效) ——刷新像素点:3840*2160 个/Vertical 一行:135KHz-7

407us,(=60Hz*2250),4400=550*8 点(3840 点=480*8 点有效) ——刷新像素点:3840 个/ Horizontal Clock:74

25MHz-13

468ns,(=135KHz*550) ——刷新像素点:8 个/Clock 以上,可参考《附录A:屏规格书信号时序特性》

二、V-by-One 信号传输规则 每个Clock(DCLK),V-by-O 接口有8 对差分对(lane0~lane7)同时传输,每对差分对负责一个Pixel;共8 个Pixels 一起传输数据

以上,可参考《附录B:屏规格书每场画面时序》与《附录C:屏规格书单区与双区的驱动方式(每一行)》

每对差分对同时串行传输4Bytes 字节(共32bits,V-by-One 传输协议有40bits);(每bit 周期0

3367ns=13

468ns/40,2,97G 带宽) 或按照公式计算:4(byte)×8×(10/8)×(594MHz/8lines)=2,97G 以上,可参考《附录D:屏规格书数据传输格式》与《附录E:V-by-O 协议文件截图》

信号最小单位为 bit,1bit 的数据长度合成眼图(1UI=0

3367ns=336

7ps),可通过眼图测试得具体信号特性; 以上,可参考《附录F:V-by-O 接口输入端眼图》

附录A :屏规格书信号时序特性 附录B :屏规格书每场画面时序 附录C :屏规格书单区与双区的驱动方式(每一行) 附录D :屏规格书数据传输格式 附录E:V-by-O 协议文件截图 附录F:V-by-O 接口