闽南理工学院 数字电子技术实验教案 1 数字电子技术 实验教案 课程名称: 数字电子技术实验 任课班级: 0920311/312/313/314/321/322 实验项目: 一 组合逻辑电路的设计(2学时) 二 译码器和编码器(2学时) 闽南理工学院 数字电子技术实验教案 2 三 数据选择器和基本RS触发器(2学时) 四 移位寄存器及其应用 (2学时) 五 计数器连接法(2学时) 六 555时基电路的应用(2学时) 七 多路抢答器的设计(设计性实验4学时) 八 考试(1学时) 共计:17学时 闽南理工学院 数字电子技术实验教案 3 实验一 组合逻辑电路的设计 一、实验目的 1、掌握异或门,半加器逻辑功能及测试

2、学会组合逻辑电路的设计与测试方法

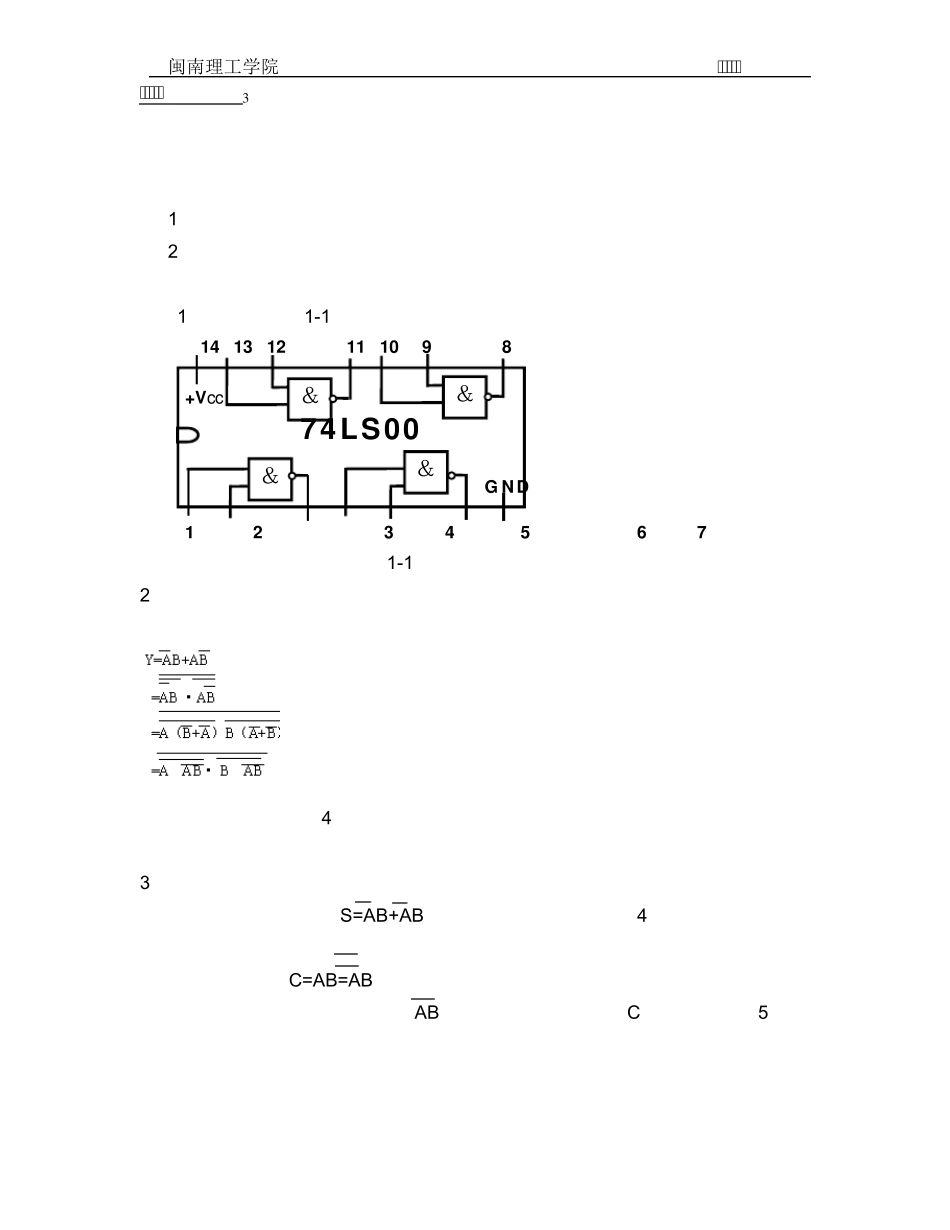

二、原理说明 1、管脚图见图 1-1 74LS00&1 2 3 4 5 6 7G ND&+Vcc14 13 12 11 10 9 8 && 图 1-1 2、用与非门构成异或门 向学生介绍清楚异或门公式如何用与非门来表示

从表达式可见用 4 个与非门即可实现异或门逻辑关系

3、用与非门构成半加器 因为半加器的本位 S=AB+AB 是一个异或逻辑,所以用 4 个与非门即可实现

半加器的进位 C=AB=AB 在前边异或门的表达式中有 AB

再求非一次即可实现 C 逻辑

可见用 5 个与非即可实现半加器

闽南理工学院 数字电子技术实验教案 4 4、用与非门构成全加器: 因为全加器的本位 S i=A⊕B⊕Ci--1=S⊕Ci--1 可见 Si 也是一个异或逻辑

所再用 4 个与非门即可实现 全加器的进位 Ci=Ci—1(A⊕B)+AB =Ci—1(A⊕B)·AB 其中 AB 是与非门可直接利用异或门中第 1 个与非门输出,而 Ci—1(A⊕B)也是一个与非门,且是第 2 个异或门中第 1 个与非门输出,可见 Ci 用一个与非门就