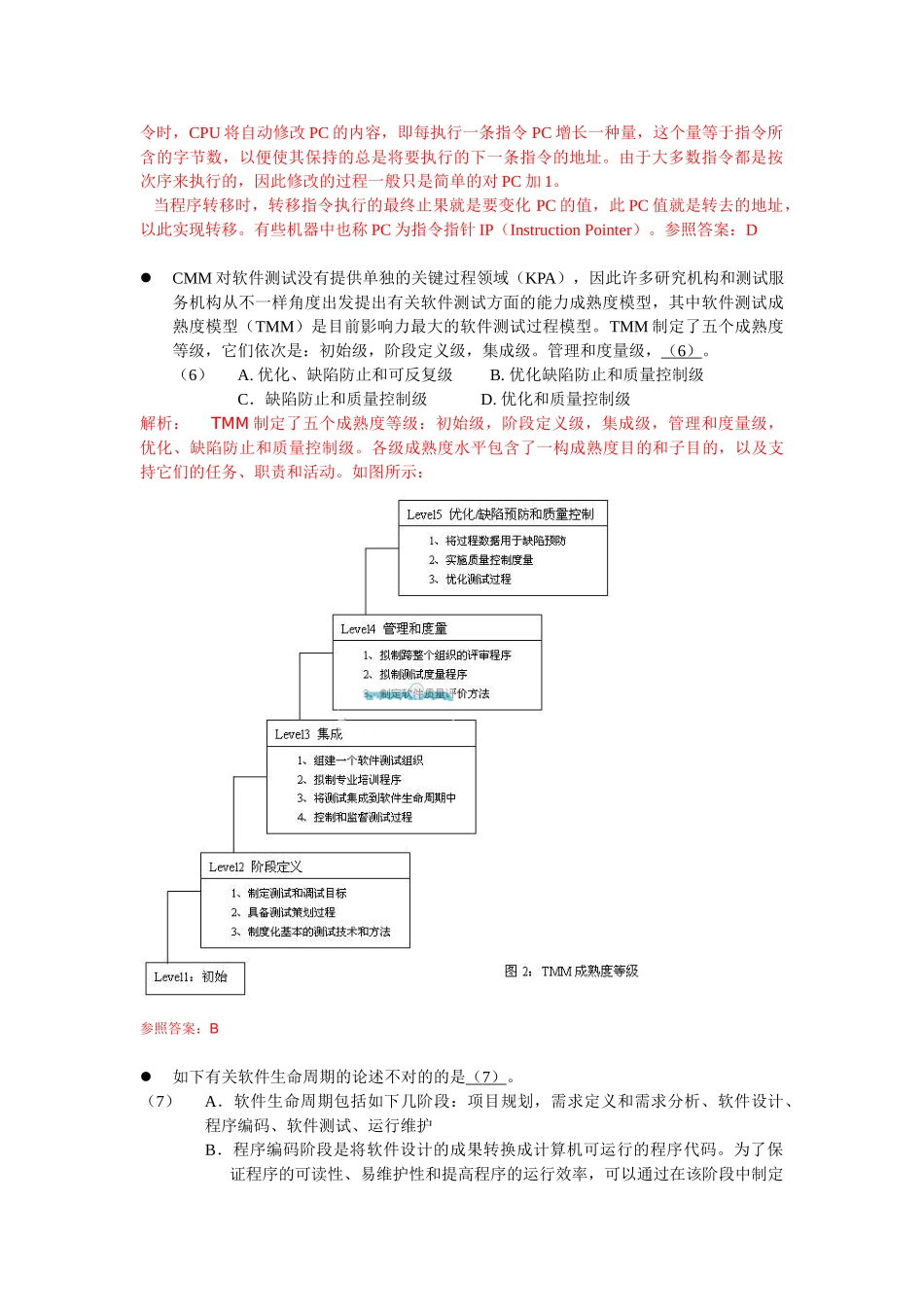

在输入输出控制措施中,采用(1)可以使得设备与主存间的数据块传送无需 CPU 干预。(1)A.程序控制输入输出 B. 中断 C.DMA D. 总线控制解析: Direct Memory Access(存储器直接访问)。这是指一种高速的数据传播操作,容许在外部设备和存储器之间直接读写数据,既不通过 CPU,也不需要 CPU 干预。整个数据传播操作在一种称为"DMA 控制器"的控制下进行的。CPU 除了在数据传播开始和结束时做一点处理外,在传播过程中 CPU 可以进行其他的工作。这样,在大部分时间里,CPU 和输入输出都处在并行操作。因此,使整个计算机系统的效率大大提高。 DMA 的概念:DMA 是在专门的硬件( DMA)控制下,实现高速外设和主存储器之间自动成批互换数据尽量减少 CPU 干预的输入/输出操作方式。一般有三种方式: ◎ 停止 CPU 访内 ◎周期挪用方式 ◎DMA 与 CPU 交替访内存 缺陷: 由于 DMA 容许外设直接访问内存,从而形成对总线的独占。参照答案: C 若某计算机采用 8 位整数补码表达数据,则运算(2)将产生溢出。(2)A.127+1 B.-127-1C.-127+1D.127-1参照答案:A若内存容量为 4GB,字长为 32.则(3)(3)A.地址总线和数据总线的宽度都为 32 B.地址总线的宽度为 30,数据总线的宽度为 32C.地址总线的宽度为 30,数据总线的宽度为 8D.地址总线的宽度为 32,数据总线的宽度为 8解析:4GB=4*2^30B=2^32B 因此地址总线和数据总线的宽度都为 32 。参照答案:A设用 2K X 4 位的存储芯片构成 16K X 8 位的存储器(地址单元为 0000H~3FFFH,每个芯片的地址空间持续),则地址单元 0B1FH 所在芯片的最大地址编号为 (4) (4)A.0000H B.2800H C.H D.0800H参照答案 D解析:2K*4 位的存储器芯片,要构成 8 位的存储器,因此在逻辑上可以把前面的存储器看作是 1K*8 的,这个是按照地址来说的。也就是说每一种单元存储芯片的地址范围是3FFH(2^10),因此看答案,0800H+3FFH=BFF,由此可以看出 0B1FH 包含在其中,因此答案为 D。或:2K*4 相称于 1K*8,需要 16 个1K=1024=0400H 也就是每片 3FF,算下来开始空间 0000,0400,0800,0C00 因此,0B1F 在0800 开头的那块上编写汇编语言程序时,下列寄存器中程序员可访问的是(5)(5)A.存储器地址寄存器(MAR) B.指令寄存器(IR)C.存储器数据寄存器(MDR)D.程序计数器(PC)解析:为了保证程序(在操作系统中理解为...