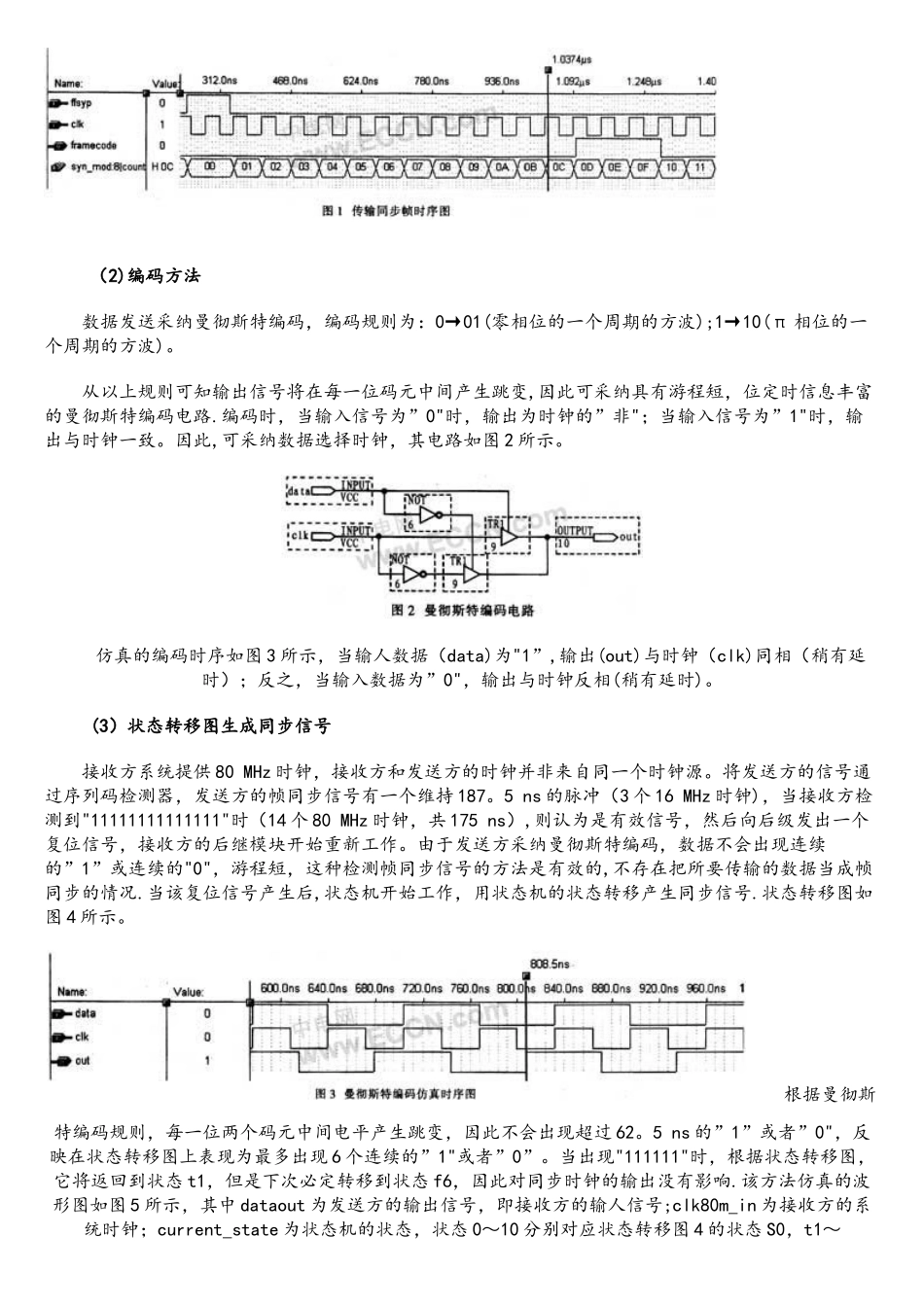

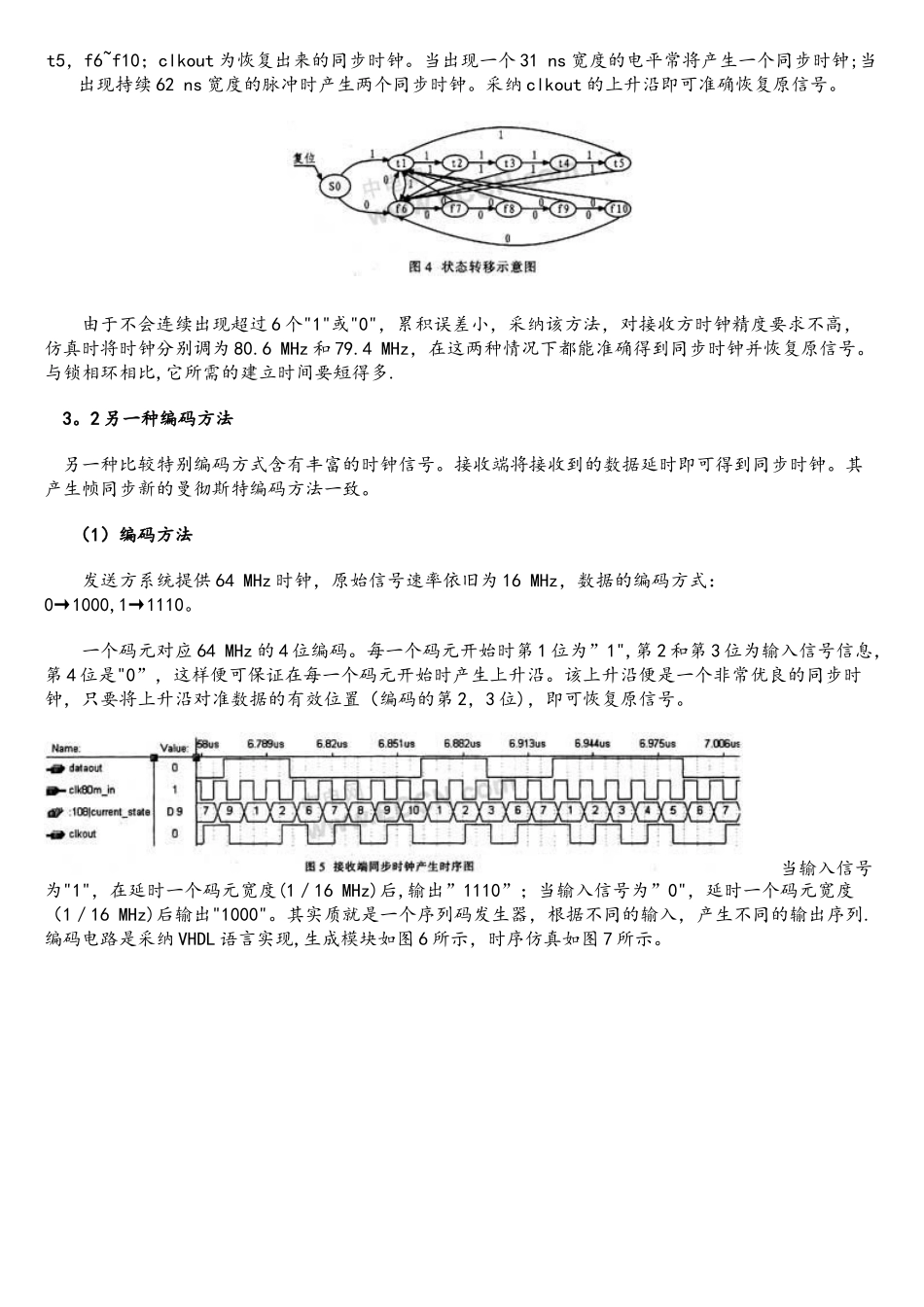

基于 FPGA 的数据高速串行通信实现1 引言 在许多实际运用的场合中,数字信号传输具有数据量大,传输速度高,采纳串行传输等特点。这就要求数据收发双方采纳合理的编解码方式及高速器件。数字信号传输一般分并行传输、串行传输两种.并行传输具有数据源和数据目的地物理连接方便,误码率低,传输速率高.但是并行传输方式要求各条线路同步,因此需要传输定时和控制信号,而其各路信号在经过转发与放大处理后,将引起不同的延迟与畸变,难以实现并行同步。若采纳更复杂的技术、设备与线路,其成本会显著上升。而高速远程数据传输一般采纳串行同步传输.传统建立准确的时钟信号的方法是采纳锁相环技术。但锁相环有若干个明显缺陷,一是其同步建立时间及调整精度即使采纳变阶的方法也很难兼顾;二是锁相环需要一个高精度高频率的本地时钟。 本文所讨论的两种串行同步传输方法,无需高频率时钟信号,就可完全数字化。采纳 Altera 公司的 ACEXlK 系列器件完成电路设计,且外围电路简单,成本低,效果好。2 主要器件介绍 编码和解码采纳 ACEXlK 系列器件 EPlK100QC208—2.ACEXlK 器件是 Altera 公司针对通信、音频处理及类似场合应用而设计的。该系列器件具有如下特性: 高性能。采纳查找表(LUT)和嵌入式阵列块(EAB)相结合的结构,适用于实现复杂逻辑功能和存储器功能,例如通信中应用的 DSP、多通道数据处理、数据传递和微控制等; 高密度。典型门数为 1 万到 10 万门,有多达 49 152 位的 RAM(每个 EAB 有 4 096 位 RAM)。 系统性能.器件内核采纳 2。5 V 电压,功耗低,其多电压引脚驱动 2.5 V、3。3 V、5.0 V 的器件,也可被这些电压所驱动,双向 I/O 引脚执行速度可达 250 MHz; 灵活的内部互联。具有快速连续式延时可预测的快速通道互连.3 实现方法 本文所述方法应用于数字音频数据实时传输。原始数字音频每一帧视频数据为并行 8 位,速率达 2 Mb/s,串行传输速度为 16 Mb/s。3。1 新的曼彻斯编码方法 这种方法是在接收端利用状态转移图的方法得到同步时钟信号。具体方法如下:(1)帧同步信号的产生 发送方系统提供 64 MHz 时钟,将其 4 分频得到 16 MHz 时钟作为系统时钟,64 MHz 时钟仅用于最后的消除信号毛刺。帧同步共 16 位,其中前 12 位为”0”,后 3 位为"1”,最后 1 位为"0"。仿真时序如图 1 所示.(2)编码方法 数据发送采纳曼彻斯特编码,编码规则为:0→01(零...