ISETCAD课程设计教学大纲ISETCAD环境的熟悉了解一.GENESISe——ISETCAD模拟工具的用户主界面1)包括GENESISe平台下如何浏览、打开、保存、增加、删除、更改项目;增加实验;增加实验参数;改变性能;增加工具流程等;2)理解基本的项目所需要使用的工具,每个工具的具体功能及相互之间的关系

二.工艺流程模拟工具LIGMENT/DIOS,器件边界及网格加密工具MDRAW1)掌握基本工艺流程,能在LIGMENT平台下完成一个完整工艺的模拟;2)在运用DIOS工具时会调用在LIGMENT中生成的*_dio

cmd文件;3)能直接编辑*_dio

cmd文件,并在终端下运行;4)掌握在MDRAW平台下进行器件的边界、掺杂、网格的编辑

三.器件仿真工具DESSIS,曲线检测工具INSPECT和TECPLOT

1)理解DESSIS文件的基本结构,例如:文件模块、电路模块、物理模块、数学模块、解算模块;2)应用INSPECT提取器件的参数,例如:MOSFET的阈值电压(Vt)、击穿电压BV、饱和电流Isat等;3)应用TECPLOT观察器件的具体信息,例如:杂质浓度、电场、晶格温度、电子密度、迁移率分布等

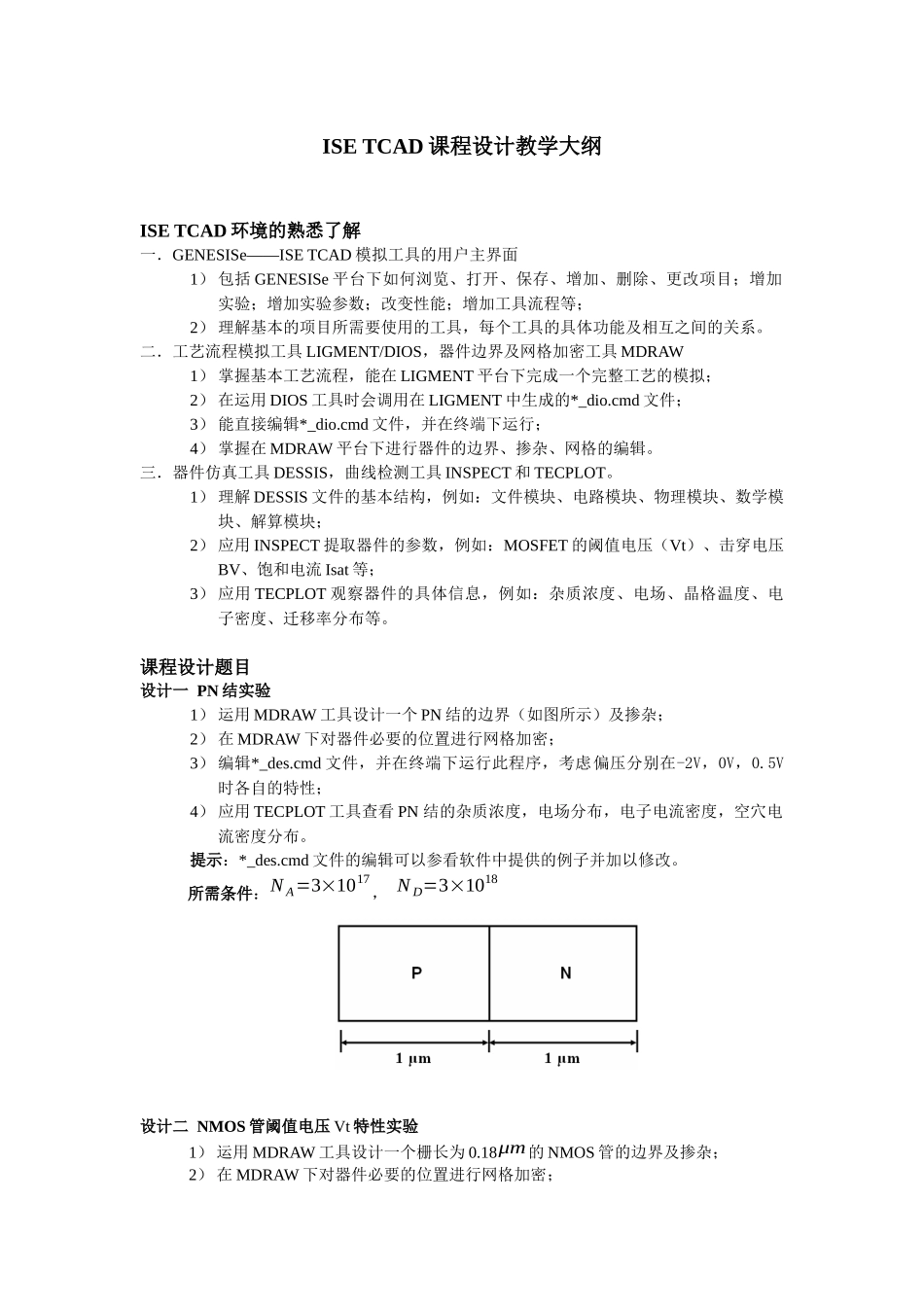

课程设计题目设计一PN结实验1)运用MDRAW工具设计一个PN结的边界(如图所示)及掺杂;2)在MDRAW下对器件必要的位置进行网格加密;3)编辑*_des

cmd文件,并在终端下运行此程序,考虑偏压分别在-2V,0V,0

5V时各自的特性;4)应用TECPLOT工具查看PN结的杂质浓度,电场分布,电子电流密度,空穴电流密度分布

提示:*_des

cmd文件的编辑可以参看软件中提供的例子并加以修改

所需条件:NA=3×1017,ND=3×1018设计二NMOS管阈值电压Vt特性实验1)运用MDRAW工具设计一个栅长为0

18μm的NMOS管的边界及掺杂;2)在MDRA