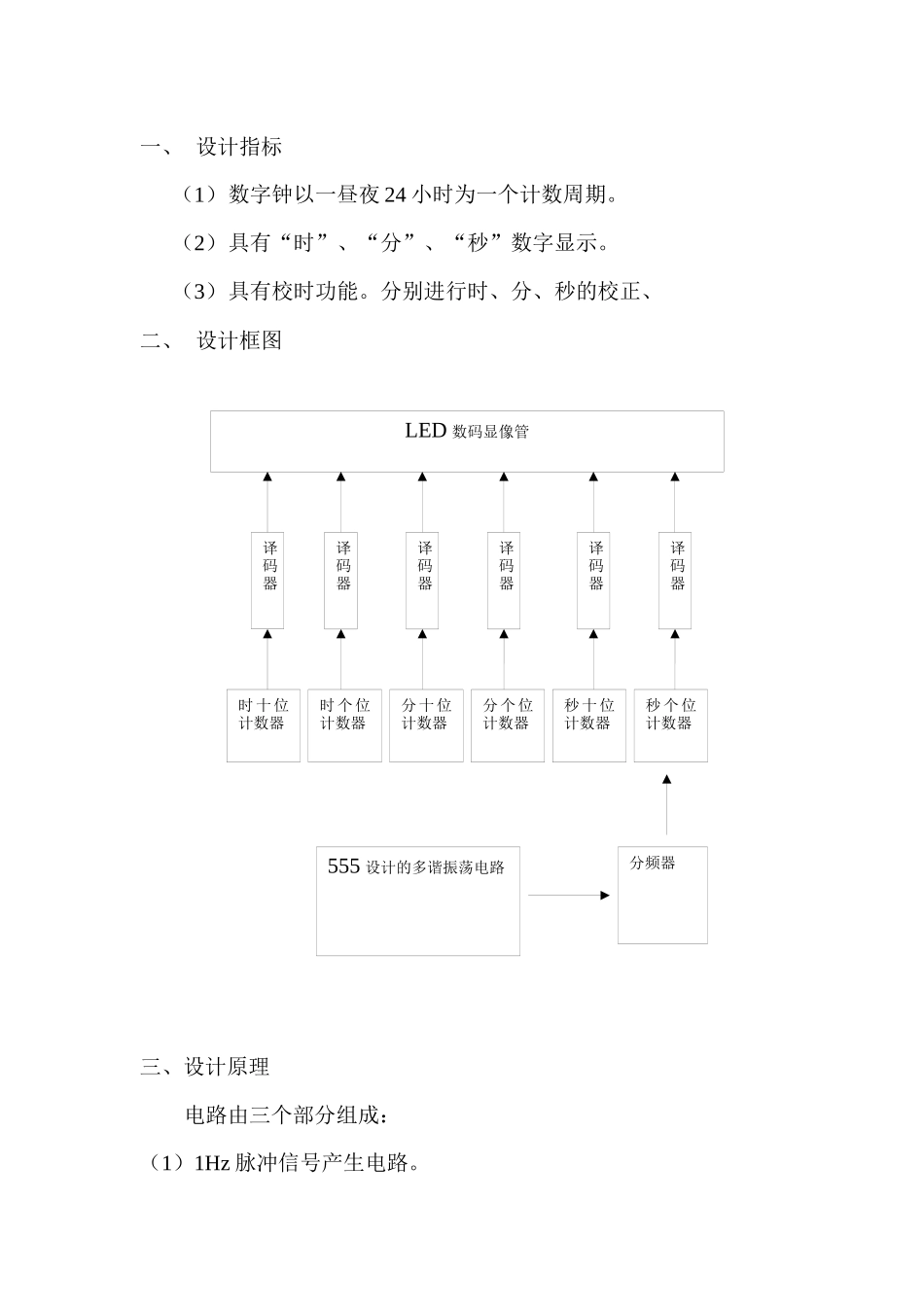

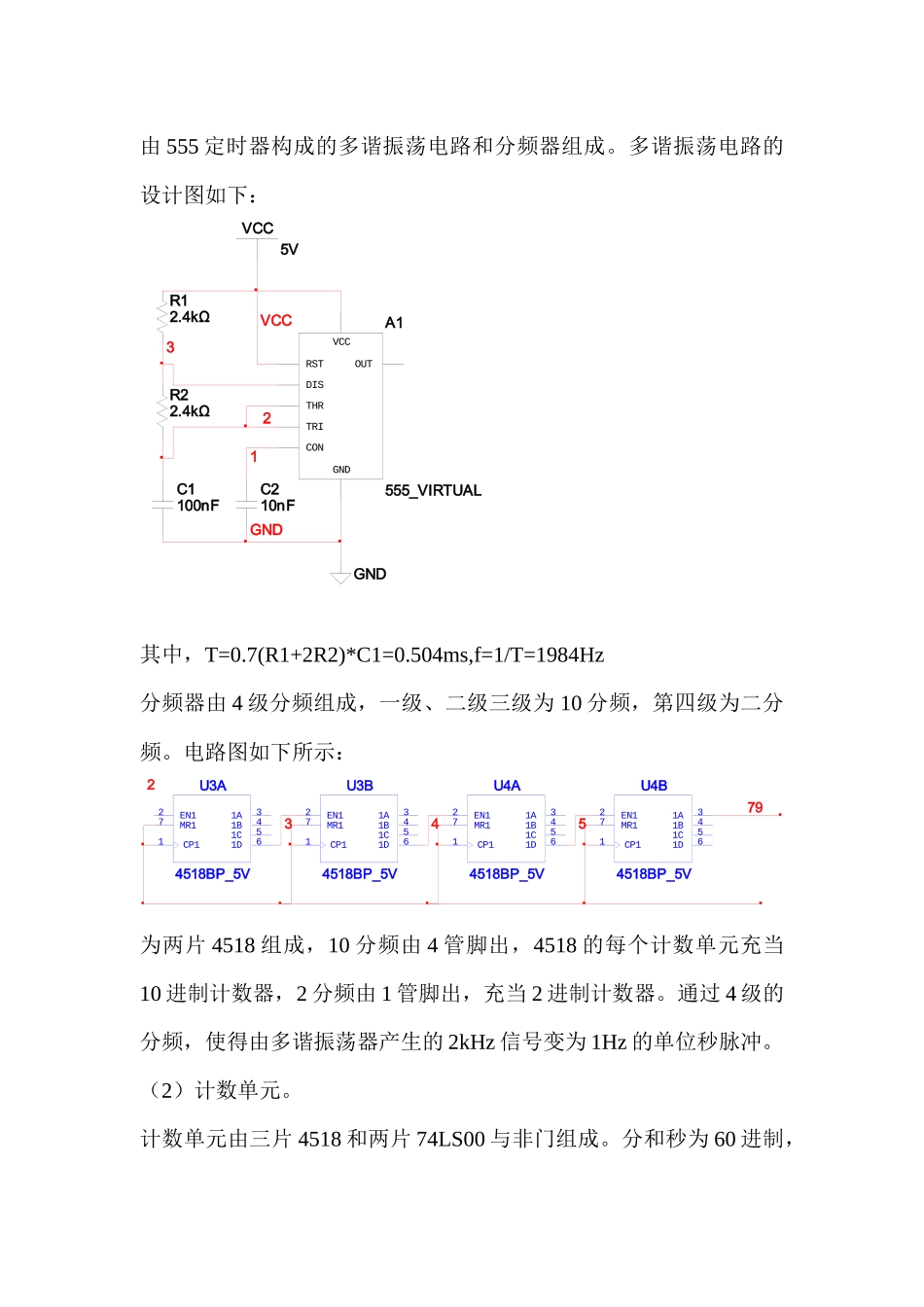

数字电子钟设计班级:电子信息科学与技术0901姓名:孙飞学号:0907090117LED数码显像管译码器译码器译码器译码器译码器译码器时十位计数器时个位计数器分十位计数器分个位计数器秒十位计数器秒个位计数器555设计的多谐振荡电路分频器一、设计指标(1)数字钟以一昼夜24小时为一个计数周期。(2)具有“时”、“分”、“秒”数字显示。(3)具有校时功能。分别进行时、分、秒的校正、二、设计框图三、设计原理电路由三个部分组成:(1)1Hz脉冲信号产生电路。由555定时器构成的多谐振荡电路和分频器组成。多谐振荡电路的设计图如下:其中,T=0.7(R1+2R2)*C1=0.504ms,f=1/T=1984Hz分频器由4级分频组成,一级、二级三级为10分频,第四级为二分频。电路图如下所示:为两片4518组成,10分频由4管脚出,4518的每个计数单元充当10进制计数器,2分频由1管脚出,充当2进制计数器。通过4级的分频,使得由多谐振荡器产生的2kHz信号变为1Hz的单位秒脉冲。(2)计数单元。计数单元由三片4518和两片74LS00与非门组成。分和秒为60进制,A1555_VIRTUALGNDDISOUTRSTVCCTHRCONTRIR12.4kΩR22.4kΩC1100nFC210nFGNDVCC5V1GNDVCC32U3A4518BP_5V1A31B41C51D6EN12MR17CP11U3B4518BP_5V1A31B41C51D6EN12MR17CP11U4A4518BP_5V1A31B41C51D6EN12MR17CP11U4B4518BP_5V1A31B41C51D6EN12MR17CP11543279其设计原理为:当十位为6时,向前一位产生进位信号,进位信号同时使十位置零,进位信号为2、3管脚通过一个与门。个位为十进制保持不变,进位信号为4管脚,接至十位的EN端。时位为24进制,其中个位进位信号依然由4管脚正常给出,十位的2管脚和个位的3管脚接一个与门同时接个位和十位的置零端,当时位为24时,两个芯片同时置零。电路如图所示:(3)显示部分显示部分由6组74LS47和LED数码显像管组成。显像管为共阳极,74LS47的abcdefg分别对应LED的各端,74LS47ABCD端分别接4518的1234端。电路如图所示:四、CD4518U5A4518BP_5V1A31B41C51D6EN12MR17CP11U6A4518BP_5V1A31B41C51D6EN12MR17CP11U7A4518BP_5V1A31B41C51D6EN12MR17CP11U8A4518BP_5V1A31B41C51D6EN12MR17CP11U9A4518BP_5V1A31B41C51D6EN12MR17CP11U20A4518BP_5V1A31B41C51D6EN12MR17CP116764626159565148U21C74LS00NU21D74LS00N697065667576U22D74LS00NU23D74LS00N77575878U24D74LS00NU25D74LS00N8081GND7268716063525553545049U1074LS47NA7B1C2D6OA13OD10OE9OF15OC11OB12OG14~LT3~RBI5~BI/RBO4U1174LS47NA7B1C2D6OA13OD10OE9OF15OC11OB12OG14~LT3~RBI5~BI/RBO4U1274LS47NA7B1C2D6OA13OD10OE9OF15OC11OB12OG14~LT3~RBI5~BI/RBO4U1374LS47NA7B1C2D6OA13OD10OE9OF15OC11OB12OG14~LT3~RBI5~BI/RBO4U1474LS47NA7B1C2D6OA13OD10OE9OF15OC11OB12OG14~LT3~RBI5~BI/RBO4U1574LS47NA7B1C2D6OA13OD10OE9OF15OC11OB12OG14~LT3~RBI5~BI/RBO4U1ABCDEFGCAU2ABCDEFGCAU16ABCDEFGCAU17ABCDEFGCAU18ABCDEFGCAU19ABCDEFGCA7876747270696867666564636261605958575655545352515049484746454443424140393837363534333231302928161512111098765797775232273181771CD4518是一个双BCD同步加计数器,由两个相同的同步4级计数器组成。CD4518引脚功能(管脚功能)如下:1CP、2CP:时钟输入端。1CR、2CR:清除端。1EN、2EN:计数允许控制端。1Q0~1Q3:计数器输出端。2Q0~2Q3:计数器输出端。Vdd:正电源。Vss:地。CD4518是一个同步加计数器,在一个封装中含有两个可互换二/十进制计数器,其功能引脚分别为1~7和9~{15}.该CD4518计数器是单路系列脉冲输入(1脚或2脚;9脚或10脚),4路BCD码信号输出(3脚~6脚;{11}脚~{14}脚)。CD4518控制功能:CD4518有两个时钟输入端CP和EN,若用时钟上升沿触发,信号由CP输入,此时EN端为高电平(1),若用时钟下降沿触发,信号由EN输入,此时CP端为低吨平(0),同时复位端Cr也保持低电平(0),只有满足了这些条件时,电路才会处于计数状态.否则没办法工作。将数片CD4518串行级联时,尽管每片CD4518属并行计数,但就整体而言已变成串行计数了。需要指出,CD4518未设置进位端,但可利用Q4做输出端。有人误将第一级的Q4端接到第二级的CP端,结果发现计...