第1页共7页编号:时间:2021年x月x日书山有路勤为径,学海无涯苦作舟页码:第1页共7页適用於消費性電子產品之低功率USB2

0PHYIPLowPowerUSB2

0PHYIPforHigh-VolumeConsumerApplicationsSynopsys,Inc

GervaisFong第2页共7页第1页共7页编号:时间:2021年x月x日书山有路勤为径,学海无涯苦作舟页码:第2页共7页概觀在計算與消費性電子領域中,USB協定已成為通用標準

設計團隊現今很少會嘗試設計自有的USB智慧財產(intellectualproperty,IP),使得此半導體IP尚不足以稱為矽商品

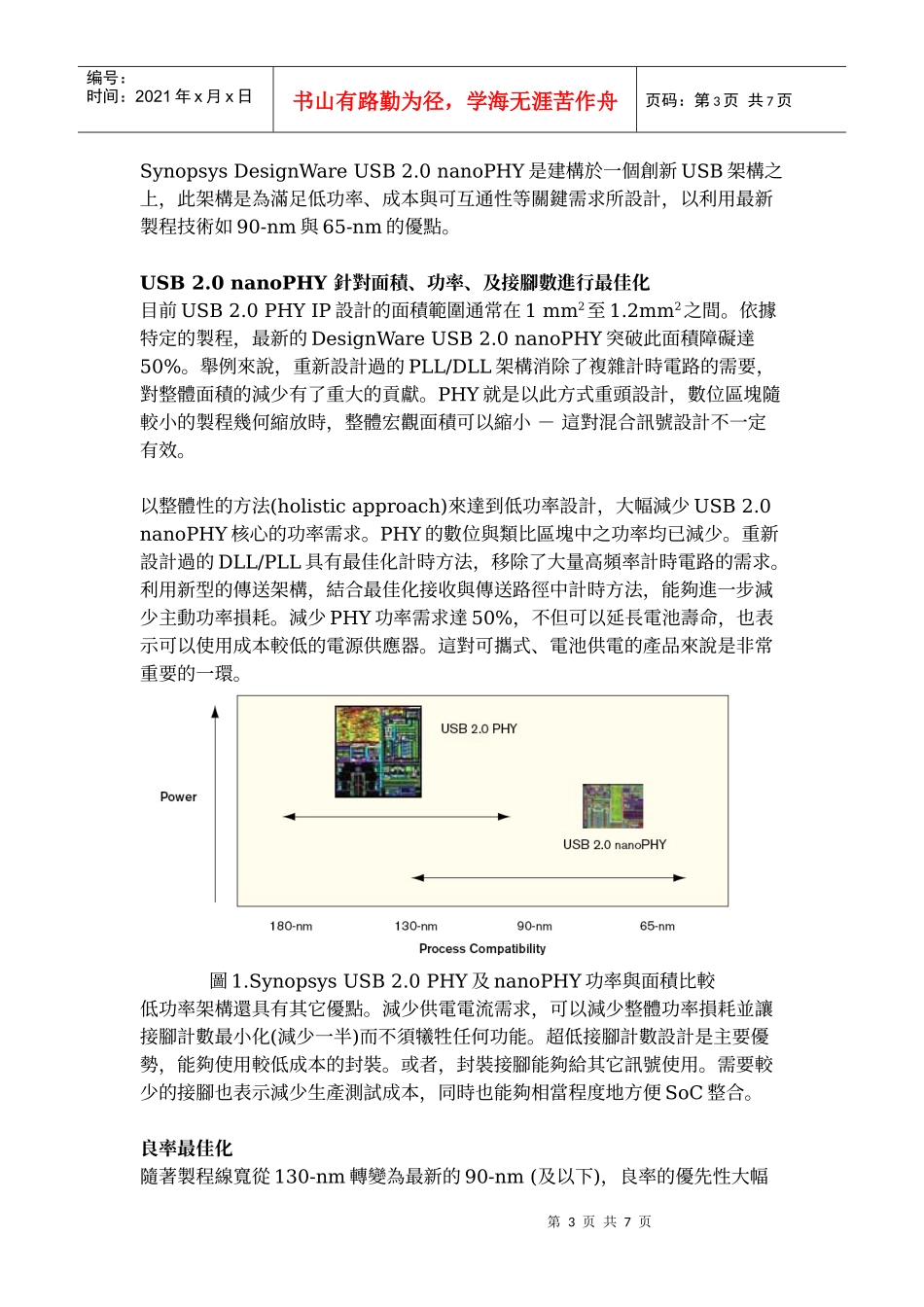

Synopsys導入第二代USB2

0PHYIP產品線(稱為DesignWare®USB2

0nanoPHY),更進一步針對行動裝置與大容量消費性應用,將低功率、面積、製造成本、及系統性能進行最佳化

此產品為設計者提供了0

13微米以下製程的高差異性USBPHY核心

引言隨著USB在行動消費性裝置中逐漸普及,設計團隊在申請IP時必須考量許多關鍵標準,例如成本、系統性能(可互通性)、可靠度、以及功率

勤勉的技術評估已成為「製造vs

購買」(makeversusbuy)決策的關鍵部份,除了最簡單的IP核心外

全球消費性電子市場的競爭動力,在於降低成本以及加速設計週期

因此,整體的設計生產力和IP所有權的總成本也是必須考慮的因素

舉例來說,雖然在大部分的專案中,避免設計重製(re-spins)是一般性的目標,但可靠度的問題,以現場失敗率(fieldfailure)來看,也會對所有權的總成本產生重大的影響

製程良率則是另一個會對總成本造成顯著影響的因素

這兩個因素都直接地受USBPHY的關鍵規格參數所影響

最後,對介面IP而言相當重要的要求就是可互通性(interoperability)

可互通性的問題不僅