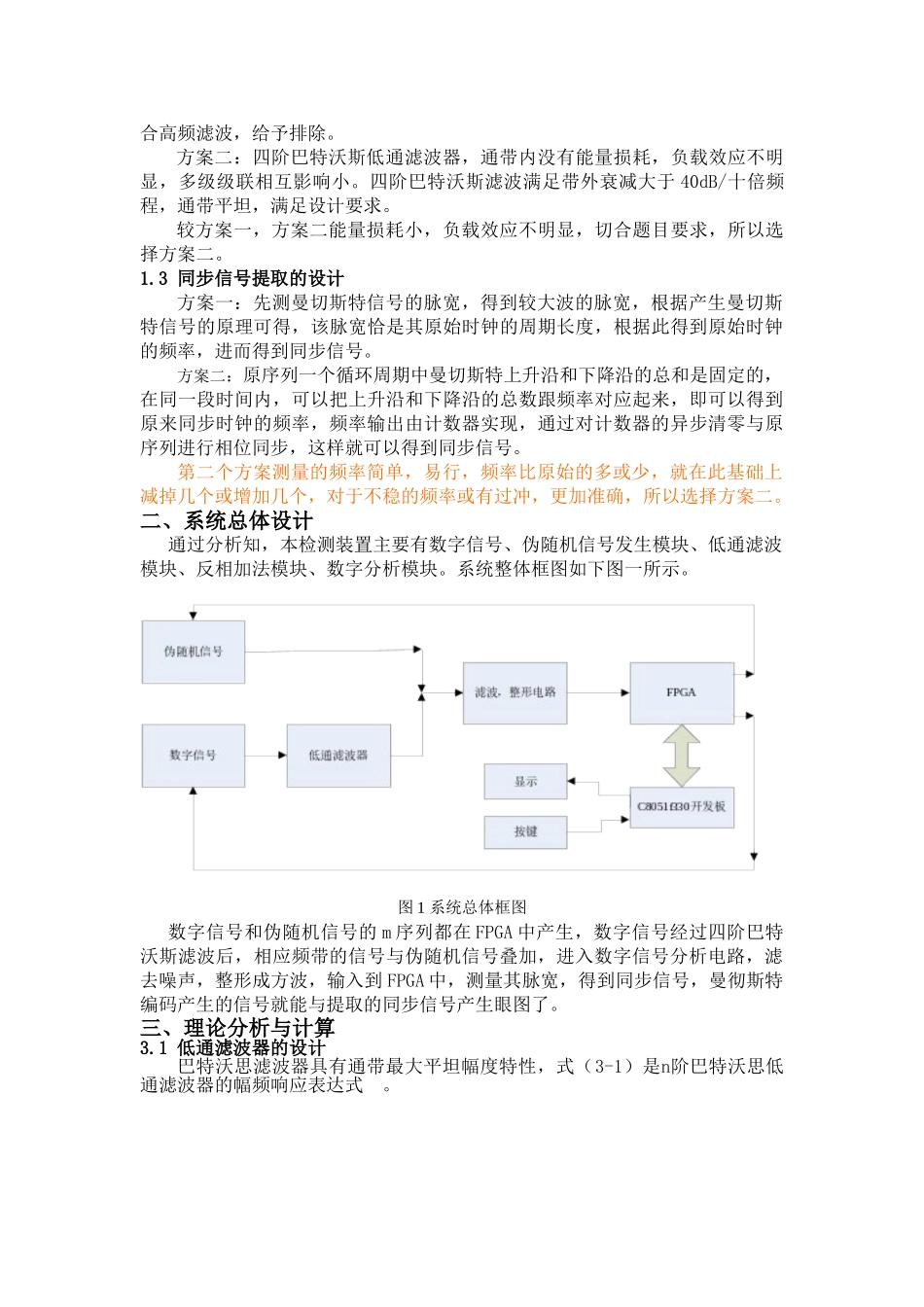

简易数字信号传输性能分析仪摘要:本文以FPGA为核心,C8051f330作为控制部分,设计了一种数字信号传输性能分析装置

它由数字信号发生器、伪随机信号发生器、模拟低通滤波器、加法电路以及数字信号分析模块等构成

数字信号发生模块和伪随机信号发生模块由FPGA产生,伪随机信号发生器和低通滤波器模拟传输信道,数字信号分析模块由滤波和整形电路构成

,此外本系统还能实现COD等功能,经测试,各项指标均能满足设计要求

信号经过四阶巴特沃斯低通滤波后,满足滤波器带外衰减不少于40dB/十倍频程的要求,两者通过反向加法电路,相互叠加后输入数字信号分析电路,此电路中有滤波,整形,产生方波后输入到FPGA中测量其脉宽,以便提取同步信号,显示出它的眼图,还能产生曼彻斯特编码,提取其信号的同步时钟,与之产生眼图,达到了数字信号传输分析的功能及其各个指标

关键字:m序列数字信号低通滤波器同步信号眼图一、方案设计与比较1

1数字信号发生器的设计:方案一:使用中规模集成电路芯片实现指定数字信号及伪随机信号的发生,然后用门电路处理后输出信号;方案二:使用大规模集成电路(如FPGA)中的移位寄存器及其门阵列实现指定信号的发生,直接输出TTL电平;方案一成本较低,但使用的芯片数量较多,硬件设计较复杂,而且进阶要求中曼彻斯特编码会增加硬件设计的负担;方案二使用现成的FPGA开发板,可较方便且较快实现指定信号的设计输出

而且可较容易实现对信号的曼彻斯特编码

所以采用方案二

2低通滤波器的设计:方案一:搭建RC无源滤波器

电路比较简单,可靠性高;但通带内的信号有能量损耗,负载效应比较明显

对于500K的截止频率,额外增加噪声,不适合高频滤波,给予排除

方案二:四阶巴特沃斯低通滤波器,通带内没有能量损耗,负载效应不明显,多级级联相互影响小

四阶巴特沃斯滤波满足带外衰减大于40dB/十倍频程,通带平坦,