XilinxCPLD系列产品1

1简介XilinxCPLD系列器件包括XC9500系列器件、CoolRunnerXPLA和CoolRunner-Ⅱ系列器件

XilinxCPLD器件可使用Foundation或ISE开发软件进行开发设计,也可使用专门针对CPLD器件的Webpack开发软件进行设计

1XC9500系列CPLD器件Xilinx公司的CPLD器件被广泛地应用在通信系统、网络、计算机系统及控制系统等电子系统中

XC9500系列CPLD器件的tPD最快达3

5ns,宏单元数达288个,可用门数达6400个,系统时钟可达到200MHz

XC9500系列器件采用快闪存储技术(FastFLASH),与E2CMOS工艺相比,功耗明显降低

XC9500系列产品均符合PCI总线规范;含JTAG测试接口电路,具有可测试性;具有在系统可编程(InSystemProgrammable,ISP)能力

XC9500系列器件分XC95005V器件、XC9500XL3

3V器件和XC9500XV2

5V器件3种类型,XC9500系列可提供从最简单的PAL综合设计到最先进的实时硬件现场升级的全套解决方案

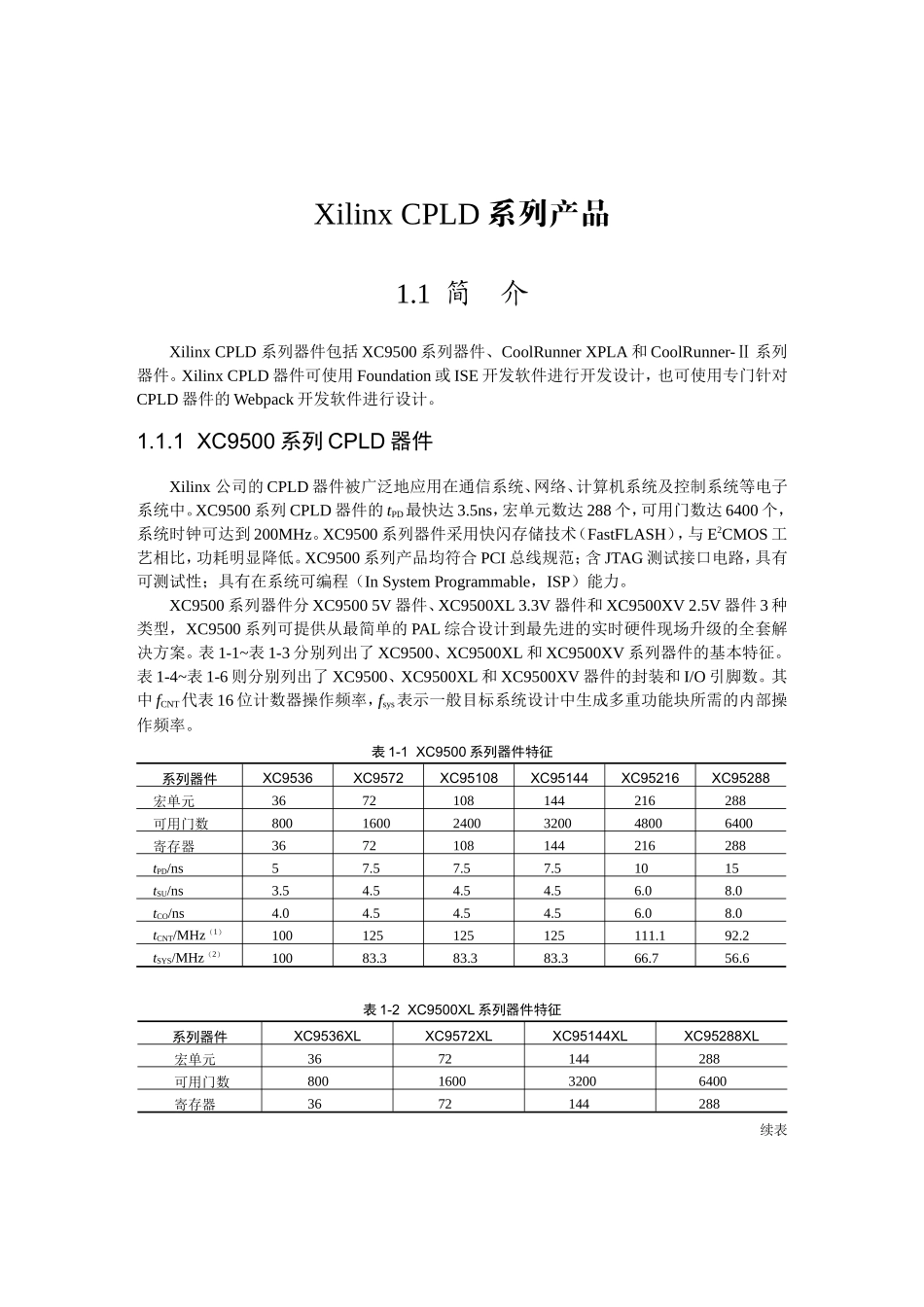

表1-1~表1-3分别列出了XC9500、XC9500XL和XC9500XV系列器件的基本特征

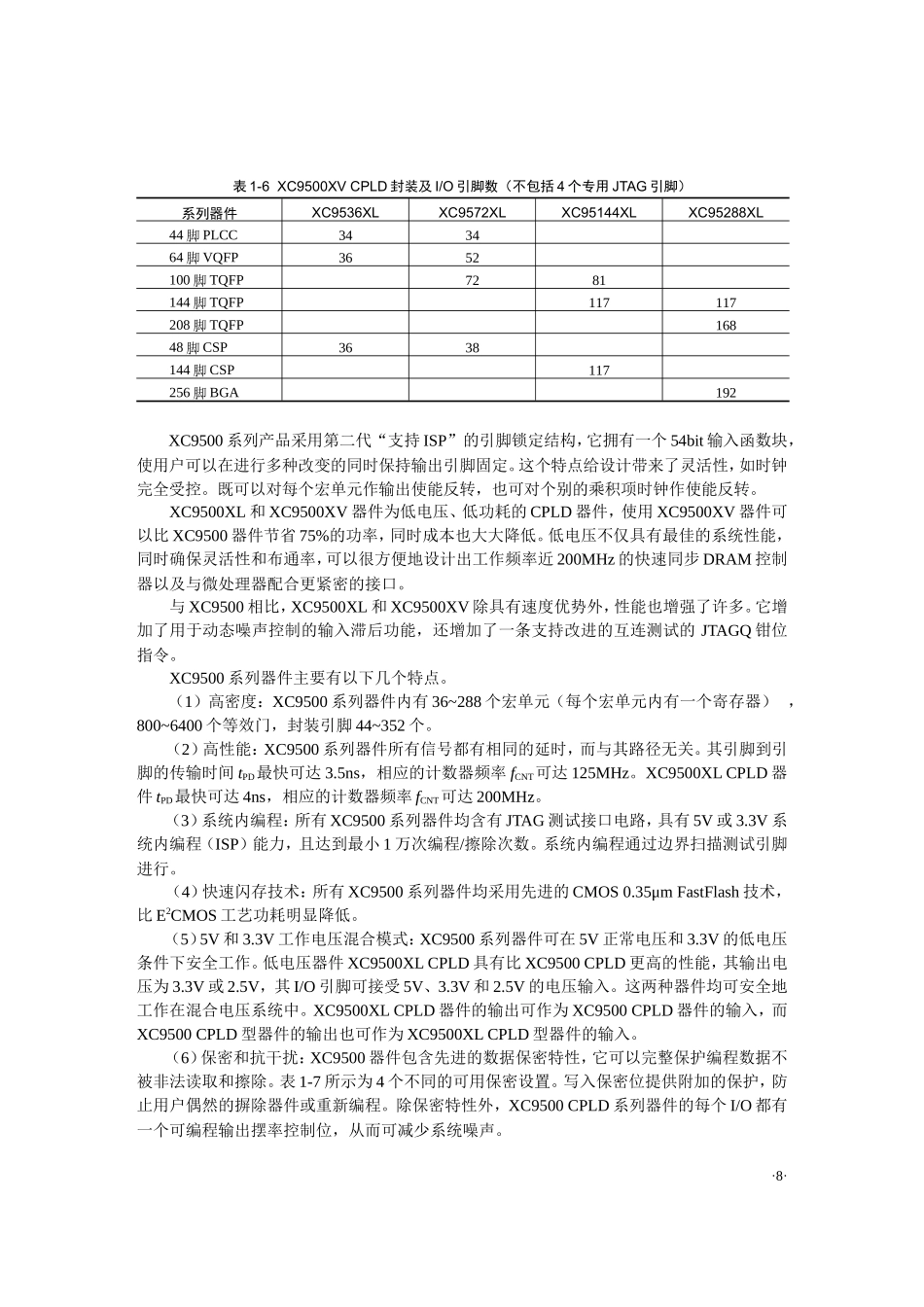

表1-4~表1-6则分别列出了XC9500、XC9500XL和XC9500XV器件的封装和I/O引脚数

其中fCNT代表16位计数器操作频率,fsys表示一般目标系统设计中生成多重功能块所需的内部操作频率

表1-1XC9500系列器件特征系列器件XC9536XC9572XC95108XC95144XC95216XC95288宏单元3672108144216288可用门数80016002400320048006400寄存器3672108144216288tPD/ns57

51015t