第四章习题四4-1填空题(1)所谓频率合成器就是利用一个晶体或几个晶体振荡器产生一系列或若干标准振荡信号

其基本思想就是利用综合或合成手段,综合晶体振荡器的频率稳定度高、准确性高和LC振荡器改变频率方便的优点,克服晶体点频工作点和LC振荡器的频率稳定度、准确度不高的特点,而形成的频率合成技术

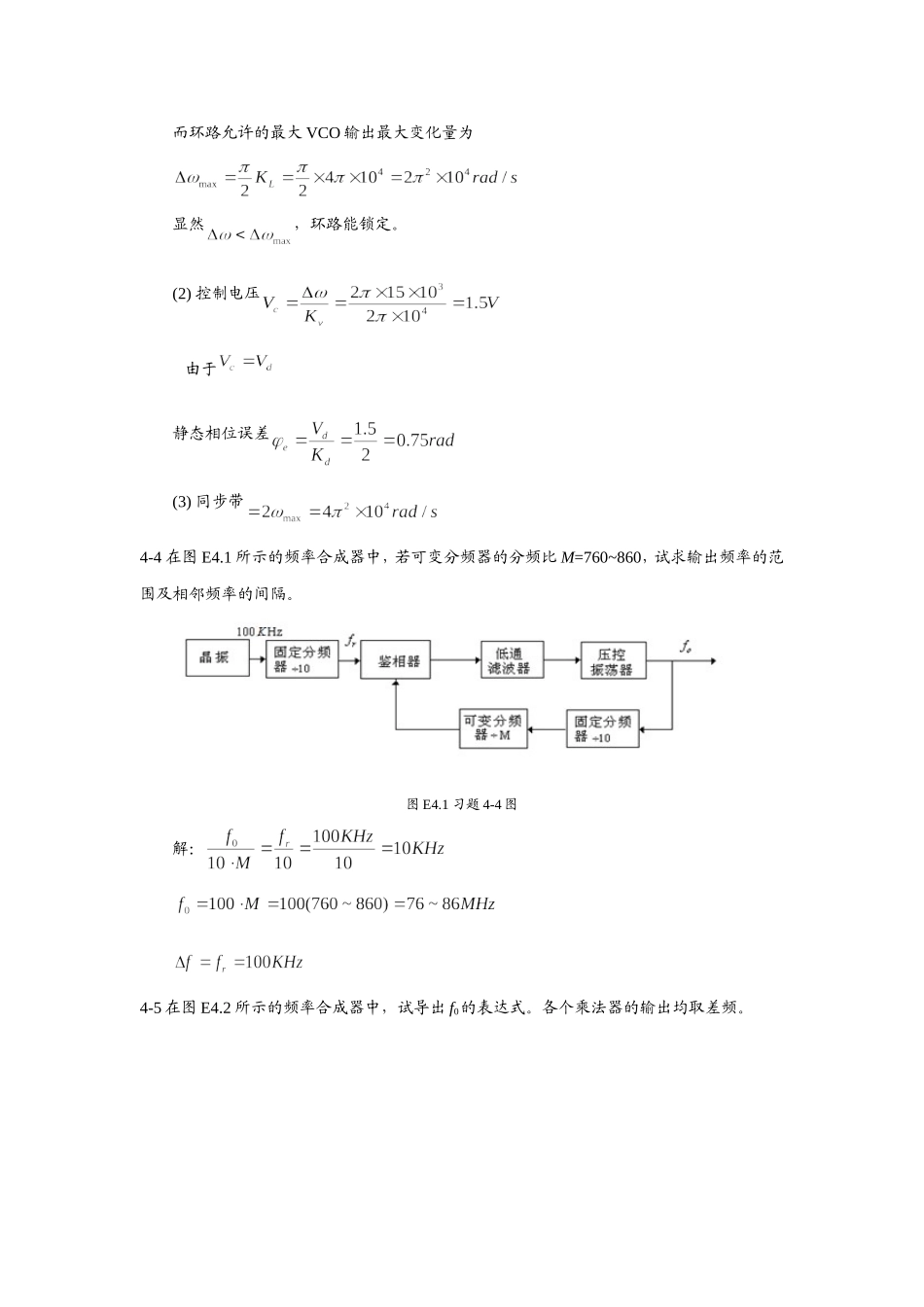

(2)在图4-1-3所示的直接频率合成器中,欲得到输出频率为76

2MHz,其开关A选取的频率为2MHz;开关B应选取的频率为6MHz;开关C应选取的频率为7MHz

(3)频率合成器的主要性能指标有频率范围、频率间隔、频率稳定度、准确度、频谱纯度、频率转换时间等

(4)小数分频是通过可变分频和多次平均来实现的

2的分频,(双模式中P/(P+1),P=7),则在10个参考频率周期中,要8次除7和2次除8

31的小数分频(双模式中P/(P+1),P=5),则在100个参考周期中,要69次除5和31次除6

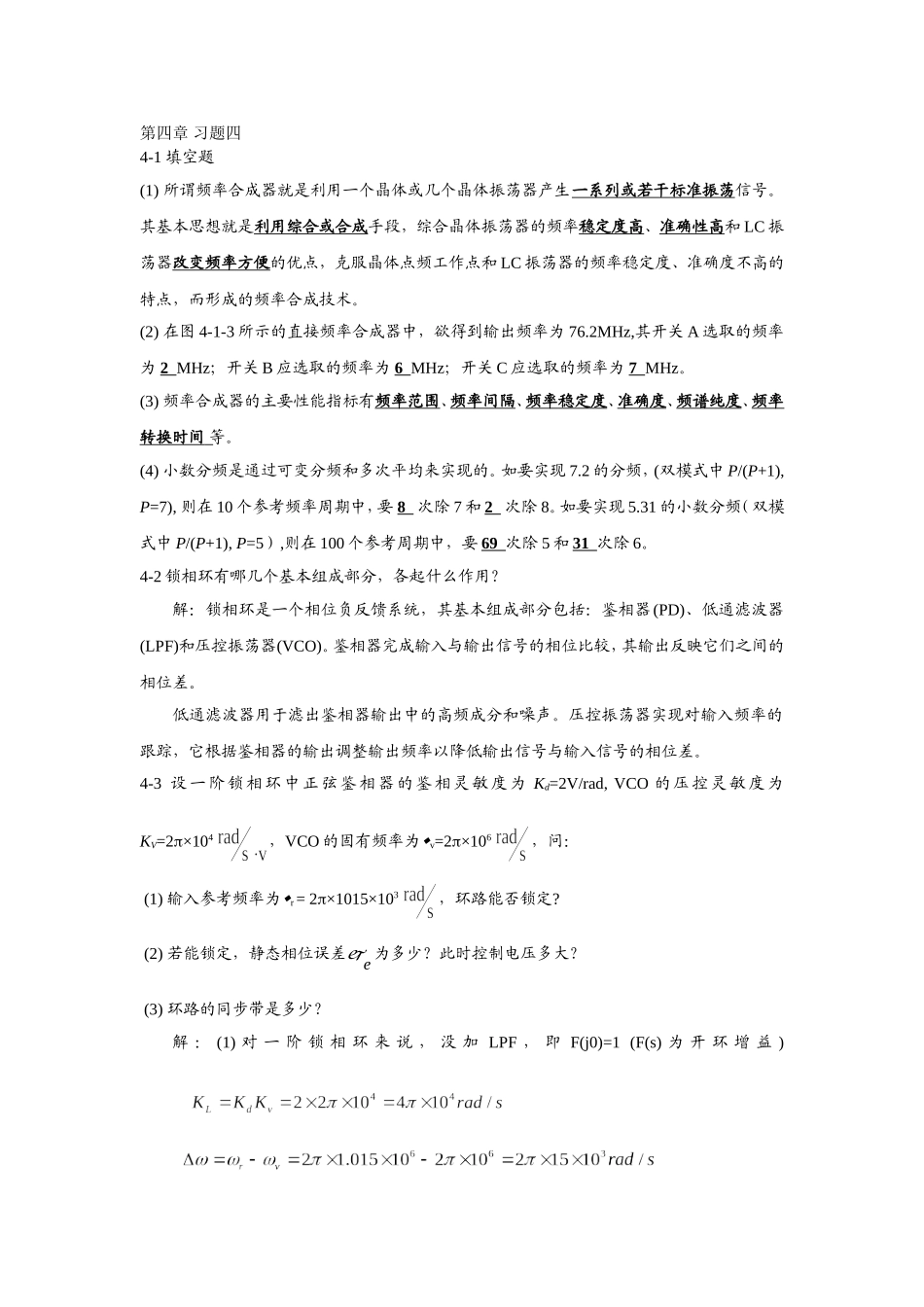

4-2锁相环有哪几个基本组成部分,各起什么作用

解:锁相环是一个相位负反馈系统,其基本组成部分包括:鉴相器(PD)、低通滤波器(LPF)和压控振荡器(VCO)

鉴相器完成输入与输出信号的相位比较,其输出反映它们之间的相位差

低通滤波器用于滤出鉴相器输出中的高频成分和噪声

压控振荡器实现对输入频率的跟踪,它根据鉴相器的输出调整输出频率以降低输出信号与输入信号的相位差

4-3设一阶锁相环中正弦鉴相器的鉴相灵敏度为Kd=2V/rad,VCO的压控灵敏度为KV=2×104,VCO的固有频率为v=2×106,问:(1)输入参考频率为r=2×1015×103,环路能否锁定

(2)若能锁定,静态相位误差e为多少

此时控制电压多大

(3)环路的同步带是多少

解:(1)对一阶锁相环来说,没加LPF,即F(j0)=1(F(s)为开环增益)而环路允许的最大VCO输出最大变化量