Pegasus 原创文档 PCB 信号完整性基础(反射,过冲及振铃原理) Pegasus Yu 本文的目的是分析电磁波在PCB 上传输时候的反射,从而阐述高速PCB 中有关信号完整性的基础问题:过冲和振铃的原理

由此可以看出,什么样的情况要关注信号完整性问题,也即什么情况下是高速互联设计

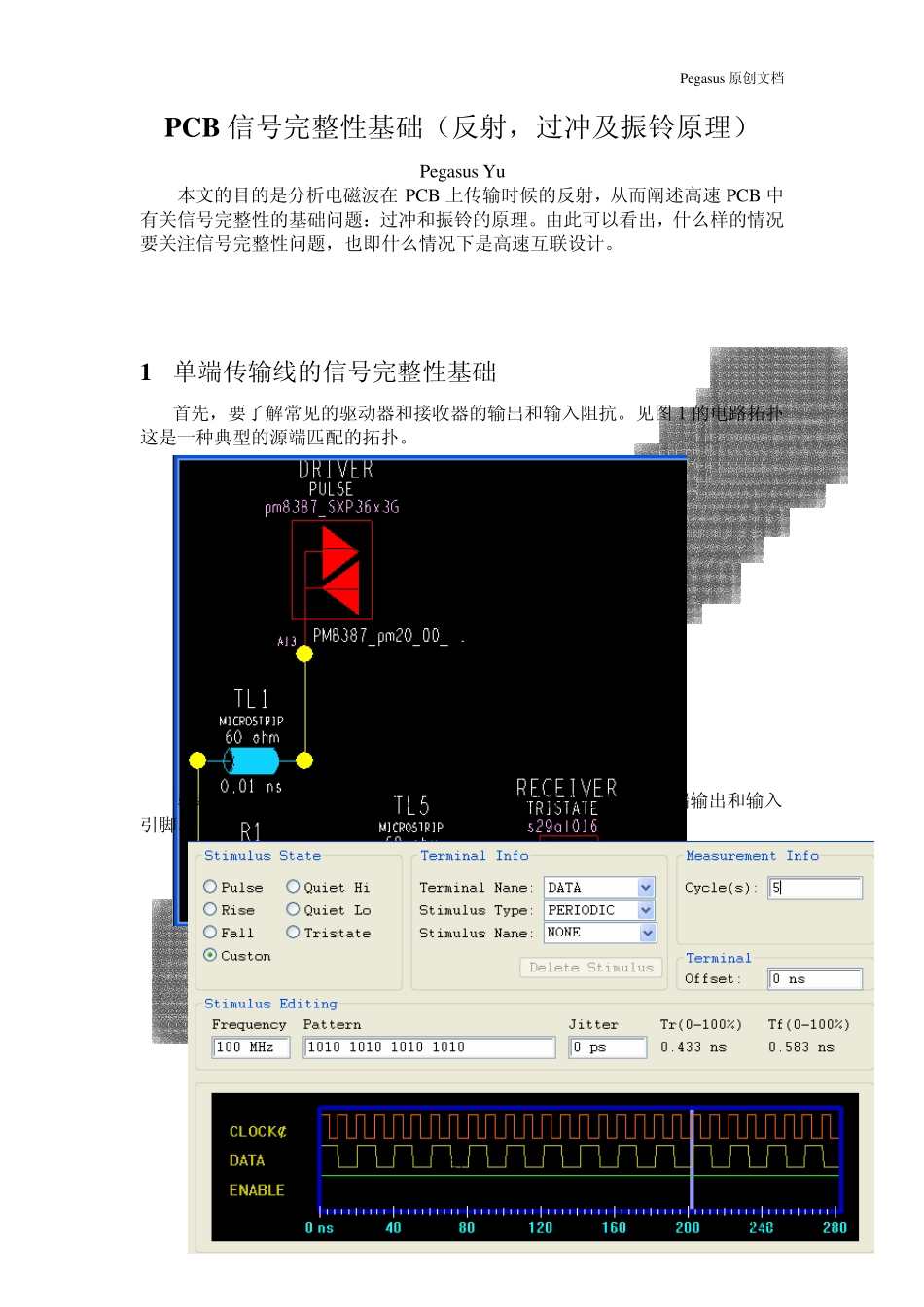

1 单端传输线的信号完整性基础 首先,要了解常见的驱动器和接收器的输出和输入阻抗

见图 1 的电路拓扑 这是一种典型的源端匹配的拓扑

图 1 驱动器输出的边沿速率见图 2

驱动器和接收器都是普通的单端输出和输入引脚

图 2 2008-02-22 Pegasus 原创文档 按照50M 时钟来仿真,当前的拓扑下,接收端的接收波形见图3

可见信号接收质量很好

没有过冲和振铃

1 驱动器的输出阻抗和接收器的输入阻抗 根据理论分析(参见《PCB 传输线电磁波传播分析(反射入射以及 TDR)》), 传输线上达到稳态后,接收端的电压为传输线上各个器件阻抗的分压(不包括传输线的特征阻抗)

在仿真中,理想传输线 TL*的特征阻抗为 60 欧姆

在上面的电路中,接收端接收的正常电压为 3

按照电磁波理论,有两种情况来使得接收端的接收电压达到需要的幅度

第一种方式是驱动器输出双倍电压 6

6V 电压,驱动端的阻抗和接收端的阻抗相等

按照反射和阻抗不匹配的关系,则当驱动端和接收端的阻抗都为 60 欧姆时,信号在传输过程中处于匹配状态,没有反射发生,同时在接收端将收到3

3V 的电压

(请考虑为什么不使得驱动器输出电压和阻抗都大一些,从而使得接收端得到 3

这是因为这样会导致驱动器端的阻抗和传输线的特征阻抗不匹配,当线路存在反射的时候,将会在驱动器端再次产生反射)

第二种方式是驱动器输出 3

3V 电压,驱动器端阻抗为 60 欧姆,等于传输线特征阻抗

这样达到接收端的初始信