冯·诺依曼体系结构和哈佛体系结构答:冯·诺依曼结构的计算机由CPU 和存储器构成,其程序和数据共用一个存储空间,程序指令存储地址和数据存储地址指向同一个存储器的不同物理位置;采用单一的地址及数据总线,程序指令和数据的宽度相同

程序计数器(PC)是CPU 内部指示指令和数据的存储位置的寄存器

冯.诺依曼结构的CPU 和微控制器品种有很多,例如Intel 公司的 8086 系列及其他 CPU,ARM 公司的 ARM7 、MIPS 公司的 MIPS 处理器等哈佛结构的主要特点是将程序和数据存储在不同的存储空间中,即程序存储器和数据存储器是两个相互独立的存储器,每个存储器独立编址、 独立访问

系统中具有程序的数据总线与地址总线,数据的数据总线与地址总线

这种分离的程序总线和数据总线可允许在一个机器周期内同时获取指令字(来自程序存储器)和操作数(来自数据存储器) ,从而提高执行速度,提高数据的吞吐率

又由于程序和数据存储器在两个分开的物理空间中,因此取指和执行能完全重叠,具有较高的执行效率

哈佛结构的 CPU 和微控制器品种有很多,除DSP 处理器外,还有摩托罗拉公司的 MC68 系列、Zilog 公司的 Z8 系列、ATMEL 公司的 AVR 系列和 ARM 公司的 ARM9 、ARM10 和 ARM11 等

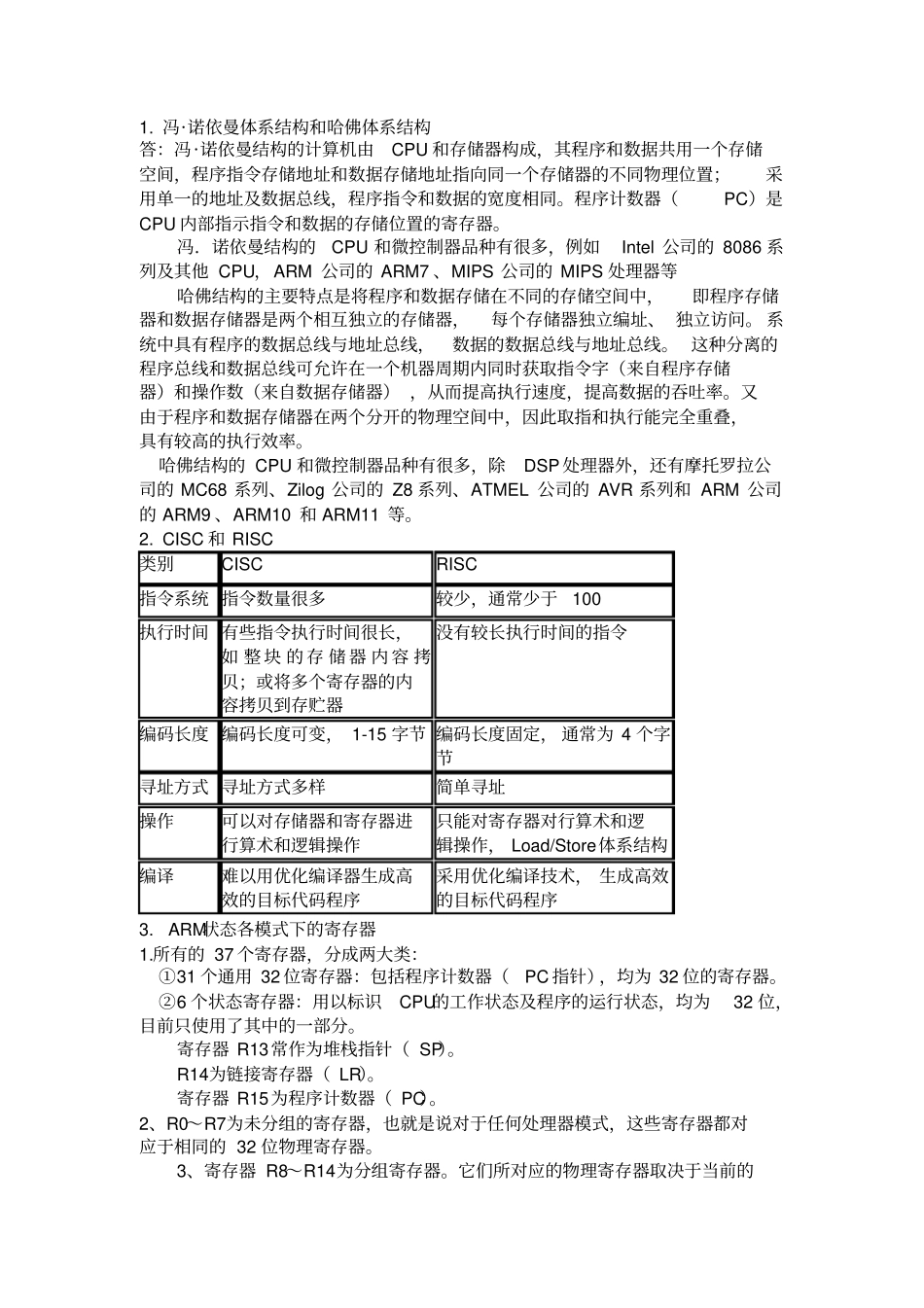

CISC 和 RISC 类别CISC RISC 指令系统 指令数量很多较少,通常少于100 执行时间 有些指令执行时间很长,如 整 块 的 存 储 器 内 容 拷贝;或将多个寄存器的内容拷贝到存贮器没有较长执行时间的指令编码长度 编码长度可变, 1-15 字节 编码长度固定, 通常为 4 个字节寻址方式 寻址方式多样简单寻址操作可以对存储器和寄存器进行算术和逻辑操作只能对寄存器对行算术和逻辑操作, Load/Store体系结构编译难以用优化编译器生成高效的目标