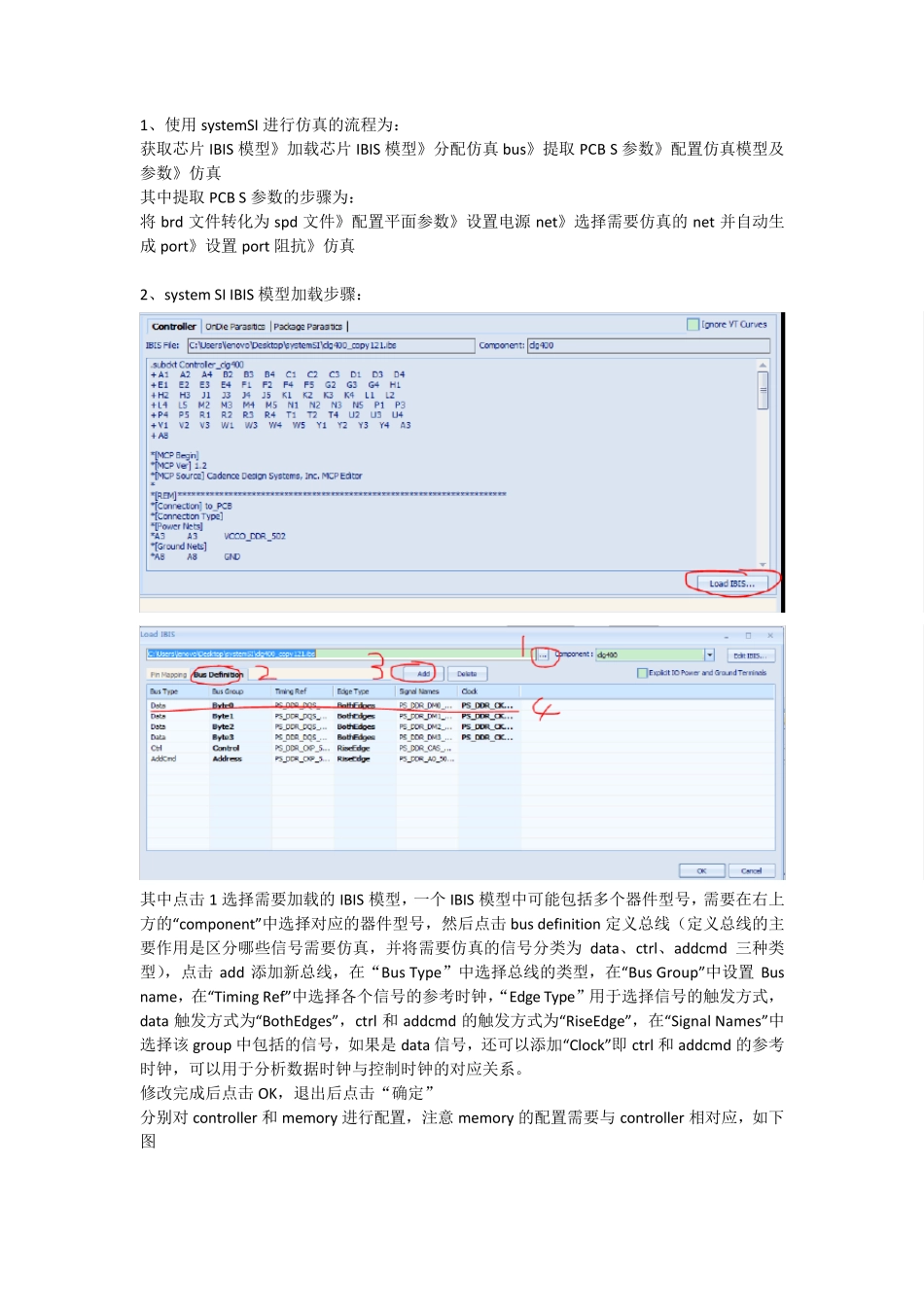

1、使用systemSI 进行仿真的流程为: 获取芯片IBIS 模型》加载芯片IBIS 模型》分配仿真bus》提取PCB S 参数》配置仿真模型及参数》仿真 其中提取PCB S 参数的步骤为: 将brd 文件转化为spd 文件》配置平面参数》设置电源net》选择需要仿真的net 并自动生成port》设置port 阻抗》仿真 2、system SI IBIS 模型加载步骤: 其中点击1 选择需要加载的IBIS 模型,一个IBIS 模型中可能包括多个器件型号,需要在右上方的“component”中选择对应的器件型号,然后点击bus definition 定义总线(定义总线的主要作用是区分哪些信号需要仿真,并将需要仿真的信号分类为data、ctrl、addcmd 三种类型),点击add 添加新总线,在“Bus Type”中选择总线的类型,在“Bus Group”中设置Bus name,在“Timing Ref”中选择各个信号的参考时钟,“Edge Type”用于选择信号的触发方式,data 触发方式为“BothEdges”,ctrl 和 addcmd 的触发方式为“RiseEdge”,在“Signal Names”中选择该 group 中包括的信号,如果是data 信号,还可以添加“Clock”即 ctrl 和 addcmd 的参考时钟,可以用于分析数据时钟与控制时钟的对应关系

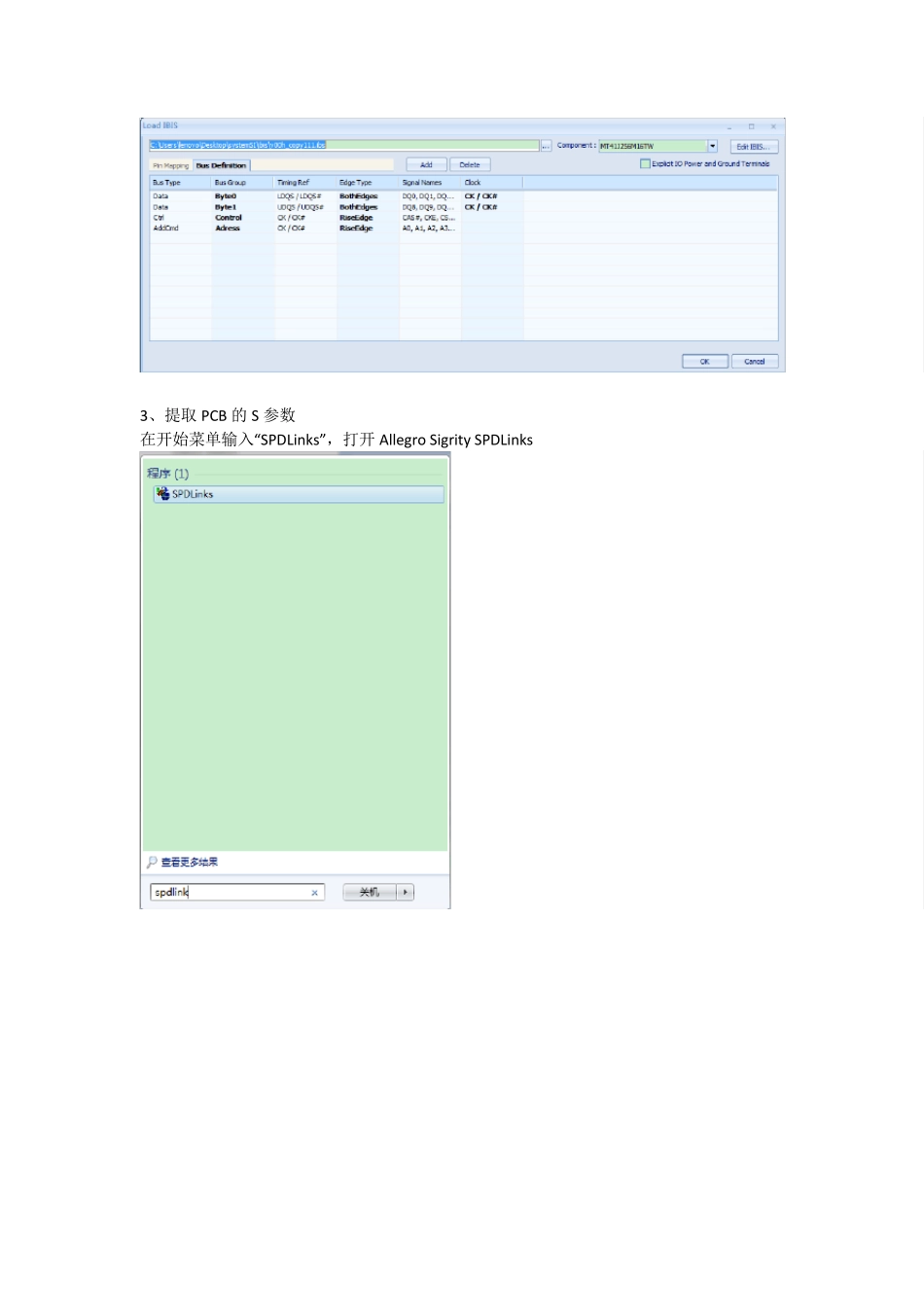

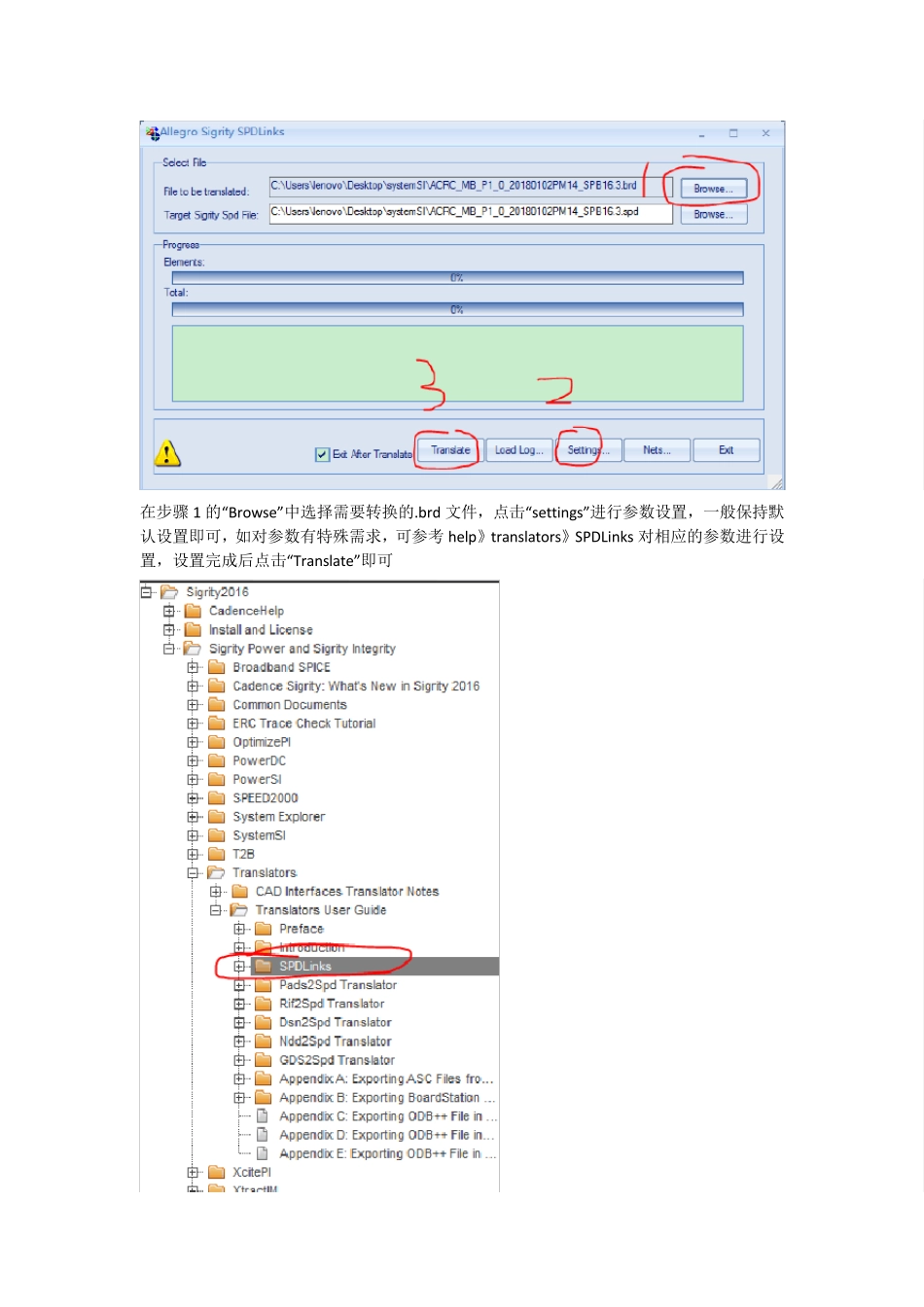

修改完成后点击OK,退出后点击“确定” 分别对controller 和 memory 进行配置,注意 memory 的配置需要与 controller 相对应,如下图 3、提取 PCB 的 S 参数 在开始菜单输入“SPDLinks”,打开 Allegro Sigrity SPDLinks 在步骤1 的“Browse”中选择需要转换的

brd 文件,点击“settings”进行参数设置,一般保持默认设置