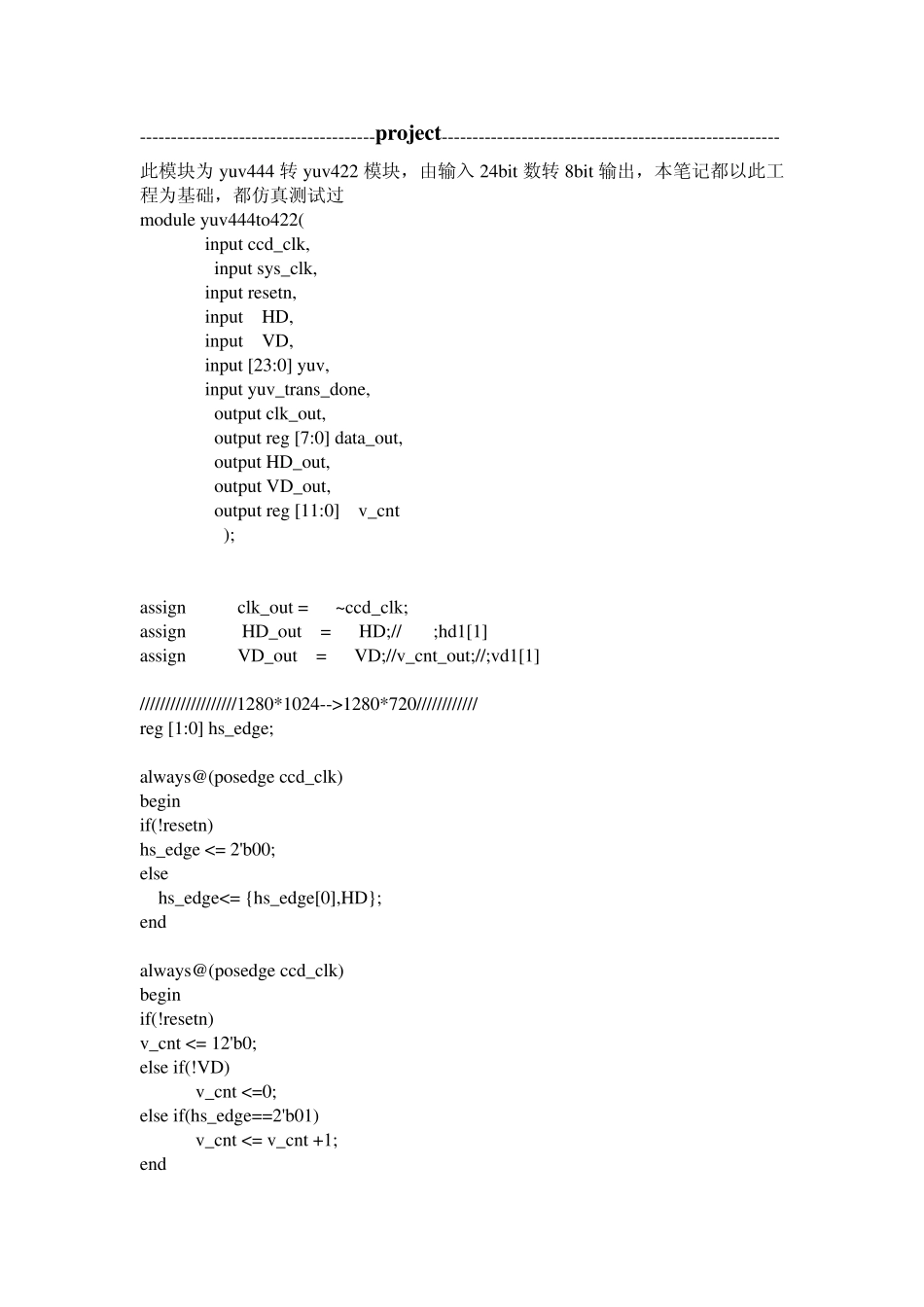

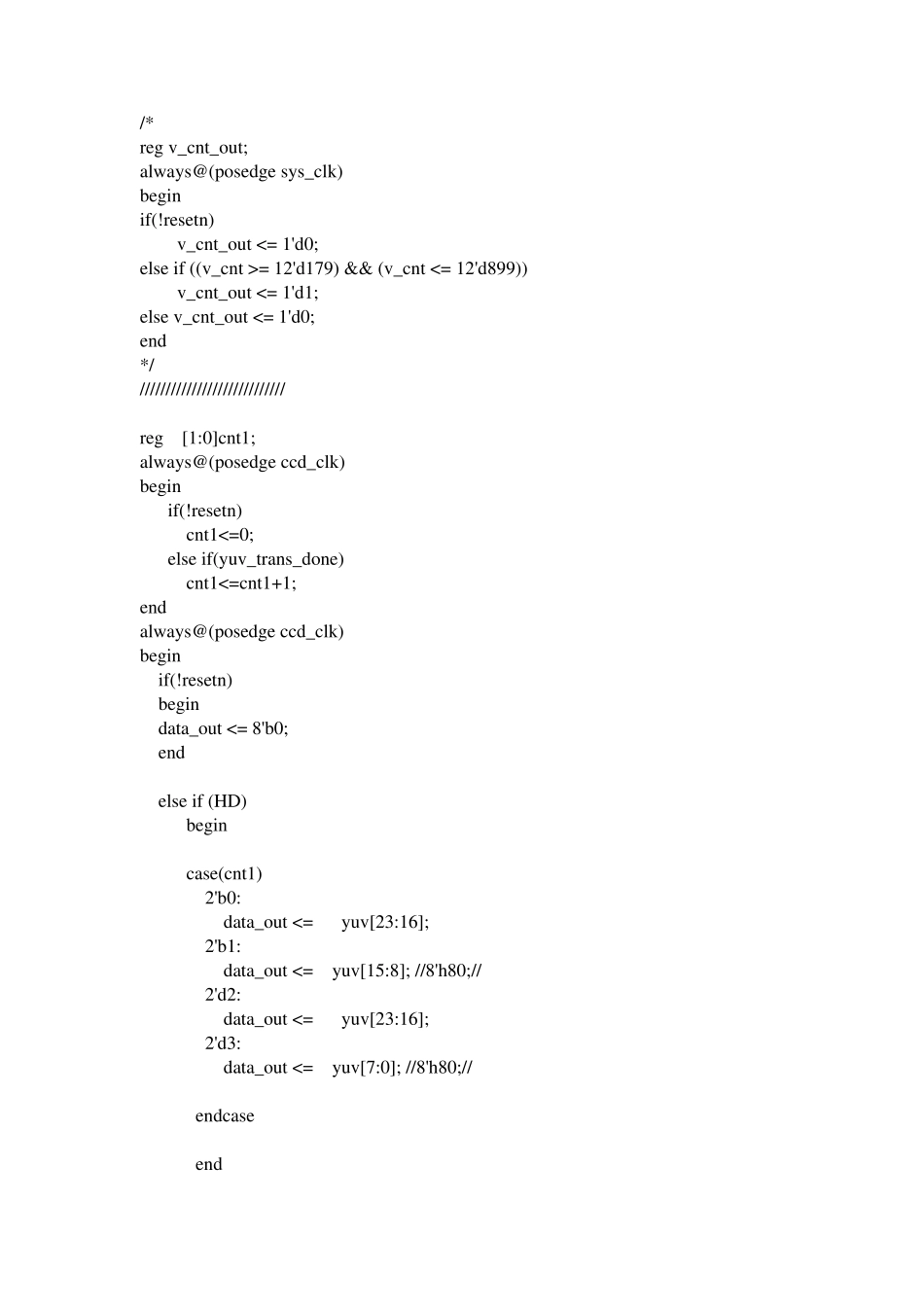

--------------------------------------project------------------------------------------------------- 此模块为 yuv444 转 yuv422 模块,由输入 24bit 数转 8bit 输出,本笔记都以此工程为基础,都仿真测试过 module yuv444to422( input ccd_clk, input sys_clk, input resetn, input HD, input VD, input [23:0] yuv, input yuv_trans_done, output clk_out, output reg [7:0] data_out, output HD_out, output VD_out, output reg [11:0] v_cnt ); assign clk_out = ~ccd_clk; assign HD_out = HD;// ;hd1[1] assign VD_out = VD;//v_cnt_out;//;vd1[1] ///////////////////1280*1024-->1280*720//////////// reg [1:0] hs_edge; always@(posedge ccd_clk) begin if(!resetn) hs_edge <= 2'b00; else hs_edge<= {hs_edge[0],HD}; end always@(posedge ccd_clk) begin if(!resetn) v_cnt <= 12'b0; else if(!VD) v_cnt <=0; else if(hs_edge==2'b01) v_cnt <= v_cnt +1; end /* reg v_cnt_out; always@(posedge sys_clk) begin if(!resetn) v_cnt_out <= 1'd0; else if ((v_cnt >= 12'd179) && (v_cnt <= 12'd899)) v_cnt_out <= 1'd1; else v_cnt_out <= 1'd0; end */ //////////////////////////// reg [1:0]cnt1; always@(posedge ccd_clk) begin if(!resetn) cnt1<=0; else if(yuv_trans_done) cnt1<=cnt1+1; end always@(posedge ccd_clk) begin if(!resetn) begin data_out <= 8'b0; end else if (HD) begin case(cnt1) 2'b0: data_out <= yuv[23:16]; 2'b1: data_out <= yuv[15:8]; //8'h80;// 2'd2: data_out <= yuv[23:16]; 2'd3: data_out <= yuv[7:0]; //8'h80;// endcase end end endmodule --------------------------------------------testbench------------------------------------------- `timescale 1 ns/ 1 ps `include "D:/tangate_quartus/yuv444to422/yuv444to422.v" module yuv444to422_vlg_tst(); reg HD; reg VD; reg ccd_clk; reg resetn; reg sys_clk; reg [23:0] yuv; reg yuv_trans_done; // wires wire HD_out; wire VD_out; wire clk_out; wire [7:0] data_out; wire [11:0] v_cnt; yuv444...