UART 收发器设计实例 UART(Universal Asynchronous Receiver Transmitter,通用异步收发器)是广泛使用的异步串行数据通信协议

下面首先介绍 UART 硬件接口及电平转换电路,分析 UART 的传输时序并利用Verilog HDL 语言进行建模与仿真,最后通过开发板与 PC 相连进行RS-232通信来测试 UART 收发器的正确性

UART 界面介绍 本节所介绍的UART 即美国电子工业协会定义的RS-232C,简称 RS-232

RS-232 的接口一般有 9 针的DB9 和 25 针的DB25,这里以 9 针为例,它的各个引脚的定义如表

DB9 的引脚定义 引脚 功能 缩写 1 资料载波检测 DCD 2 数据接收 RXD 3 资料发送 TXD 4 资料终端准备 DTR 5 地 GND 6 资料设备准备就绪 DSR 7 发送请求 RTS 8 清除发送 CTS 9 地 GND 由于 RS-232 的电气特性与 FPGA 引脚不相同,因此它们之间不能直接相连,对于 RS-232的数据线,当为逻辑“1”时,对应电平是-15V~-3V;当为逻辑“0”时,对应电平是15V~3V

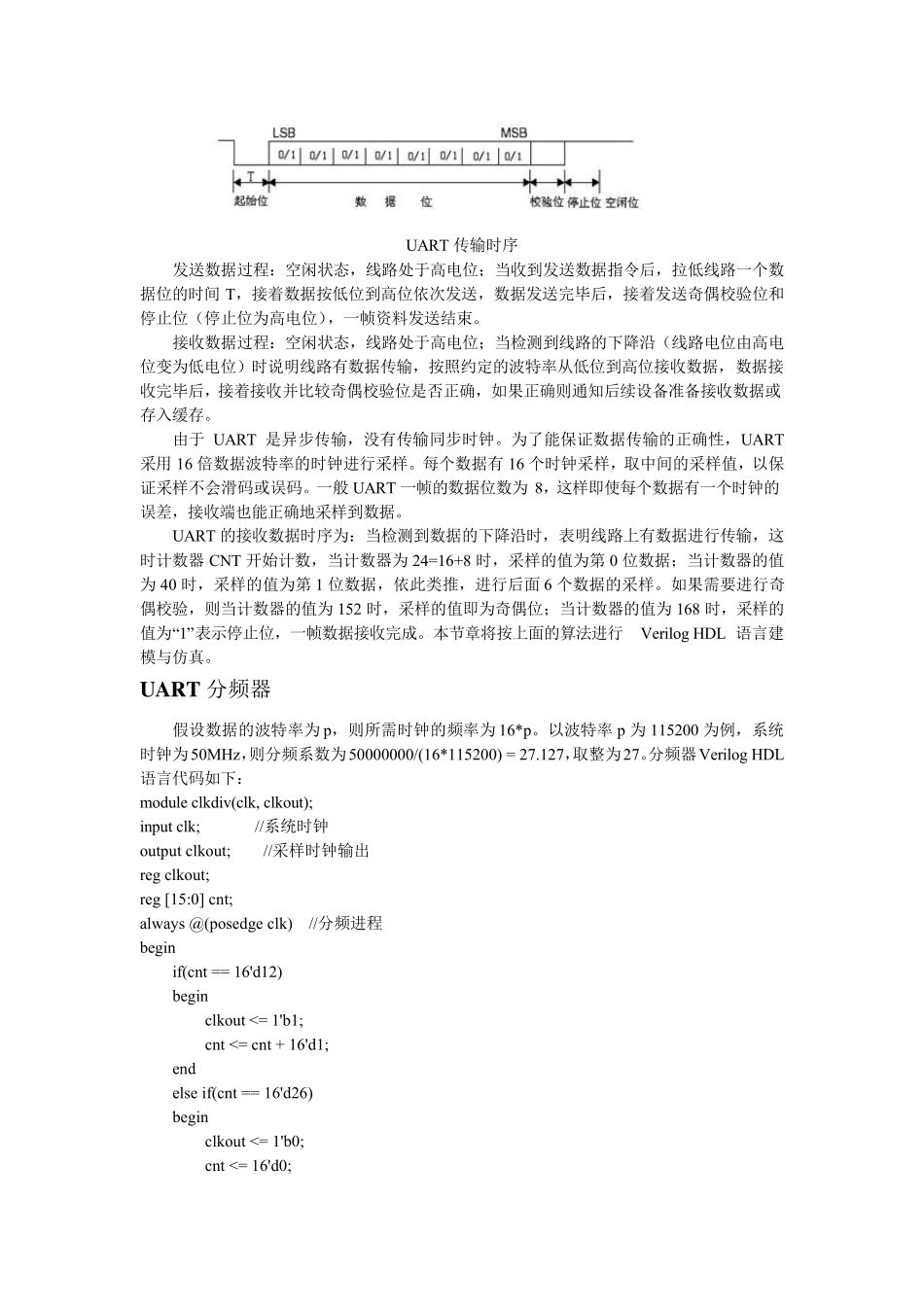

因此,与 FPGA 相连之前必须进行电平转换,转换原理图如图所示 RS-232 电平转换原理图 UART 传输时序 UART 传输时序如图 UART 传输时序 发送数据过程:空闲状态,线路处于高电位;当收到发送数据指令后,拉低线路一个数据位的时间T,接着数据按低位到高位依次发送,数据发送完毕后,接着发送奇偶校验位和停止位(停止位为高电位),一帧资料发送结束

接收数据过程:空闲状态,线路处于高电位;当检测到线路的下降沿(线路电位由高电位变为低电位)时说明线路有数据传输,按照约定的波特率从低位到高位接收数据,数据接收完毕后,接着接收并比较奇偶校验位是否正确,如