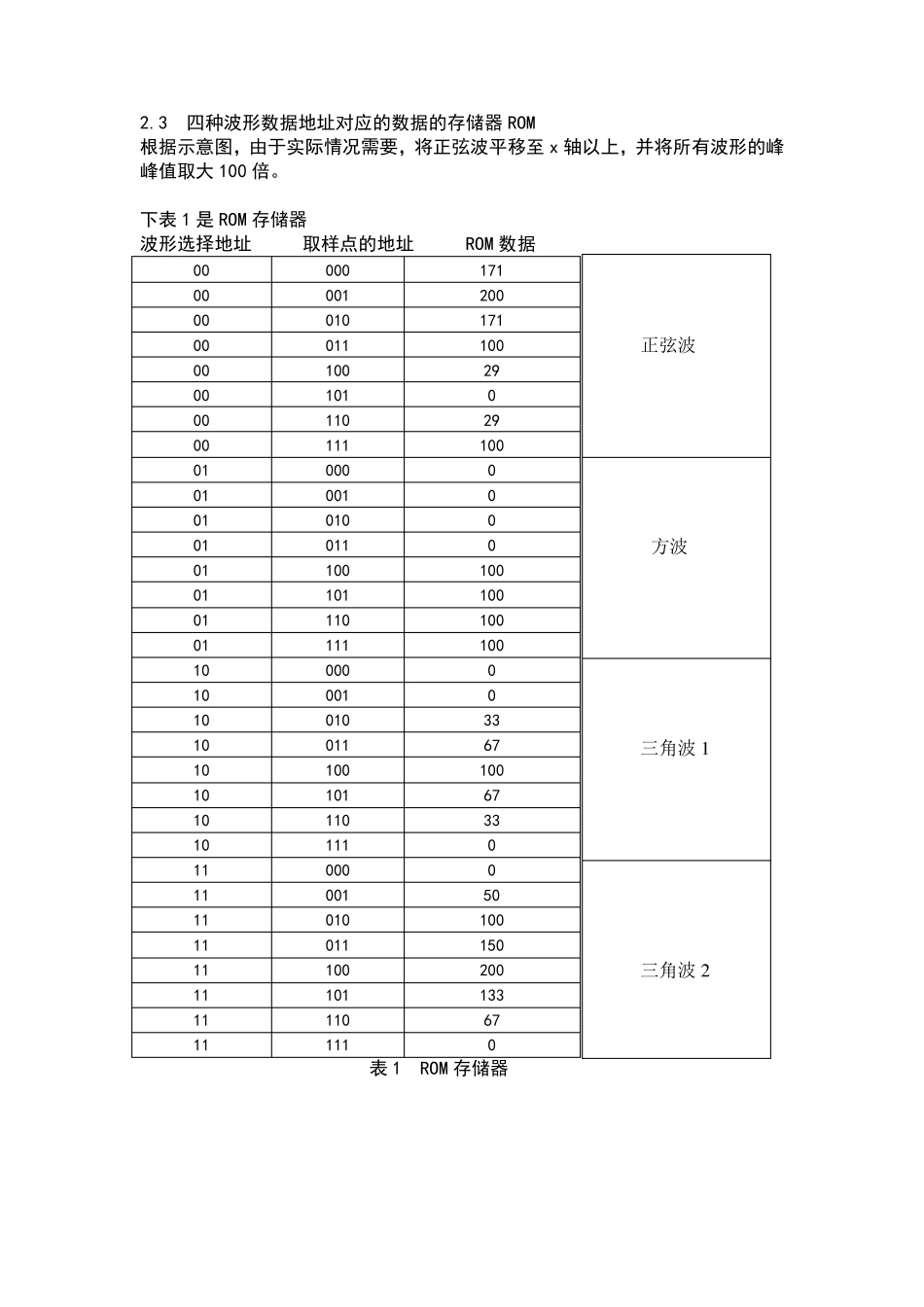

一、实验目的 使用 Verilog 软件编写四种波形任意发生器的源代码,用 modelsim 软件进行仿真测试,进一步强化 Verilog,modelsim 软件的编程能力为进一步的编程学习打下良好的基础。 二、实验原理 2.1 该任意波形发生器要实现三个功能: (1)通过计数器并结合拼接操作产生四种波形正弦波,方波,三角波 1,三角波形的 5 位数据地址。 (2).设定 ROM 中对应波形地址地址的 8 位数值,将所有波形数值存储到 ROM中。 (3).设定 2 位的波形选择开关端口。 2bit 00000~00111 01000~01111 3bit data[7:0] 10000~10111 11000~11111 图 1 整体设计方案 2.2 四种波形要在一个周期内等间隔取 8 个点,定义对应的数据,下图为示意图,由于编程序需要,数据会进行相应的修改。 图 2 四种波形一个周期内的取样示意图 地址发生器(0-7) 正弦波 方波 三角波1 三角波2 clk reset 波形选择 1 -1 1 1 正弦波 方波 三角波1 三角波2 y x x 8 8 y 0 0 y x 8 1 2.3 四种波形数据地址对应的数据的存储器ROM 根据示意图,由于实际情况需要,将正弦波平移至x 轴以上,并将所有波形的峰峰值取大100 倍。 下表 1 是 ROM 存储器 波形选择地址 取样点的地址 ROM 数据 00 000 171 00 001 200 00 010 171 00 011 100 00 100 29 00 101 0 00 110 29 00 111 100 01 000 0 01 001 0 01 010 0 01 011 0 01 100 100 01 101 100 01 110 100 01 111 100 10 000 0 10 001 0 10 010 33 10 011 67 10 100 100 10 101 67 10 110 33 10 111 0 11 000 0 11 001 50 11 010 100 11 011 150 11 100 200 11 101 133 11 110 67 11 111 0 表 1 ROM 存储器 三角波 2 方波 正弦波 三角波 1 三、实验内容 3.1 任意波形发生器 verilog 程序代码: module wave(data,clk,add1,reset);//顶层模块端口定义 output[7:0]data; input clk,reset; input[1:0] addr1; Wire[1:0] addr1; wire clk,reset;//输入输出变量定义 ADDR 4(addr,clk,addr1,reset);//地址发生器模块调用 rom 1(addr,data);//ROM存储器模块调用 endmodule module ADDR(addr,clk,addr1,reset); output[4:0] addr; input clk,reset; wire clk,reset; reg[2:0] addr2; wire[1:0] addr1; reg[4:0] addr;...