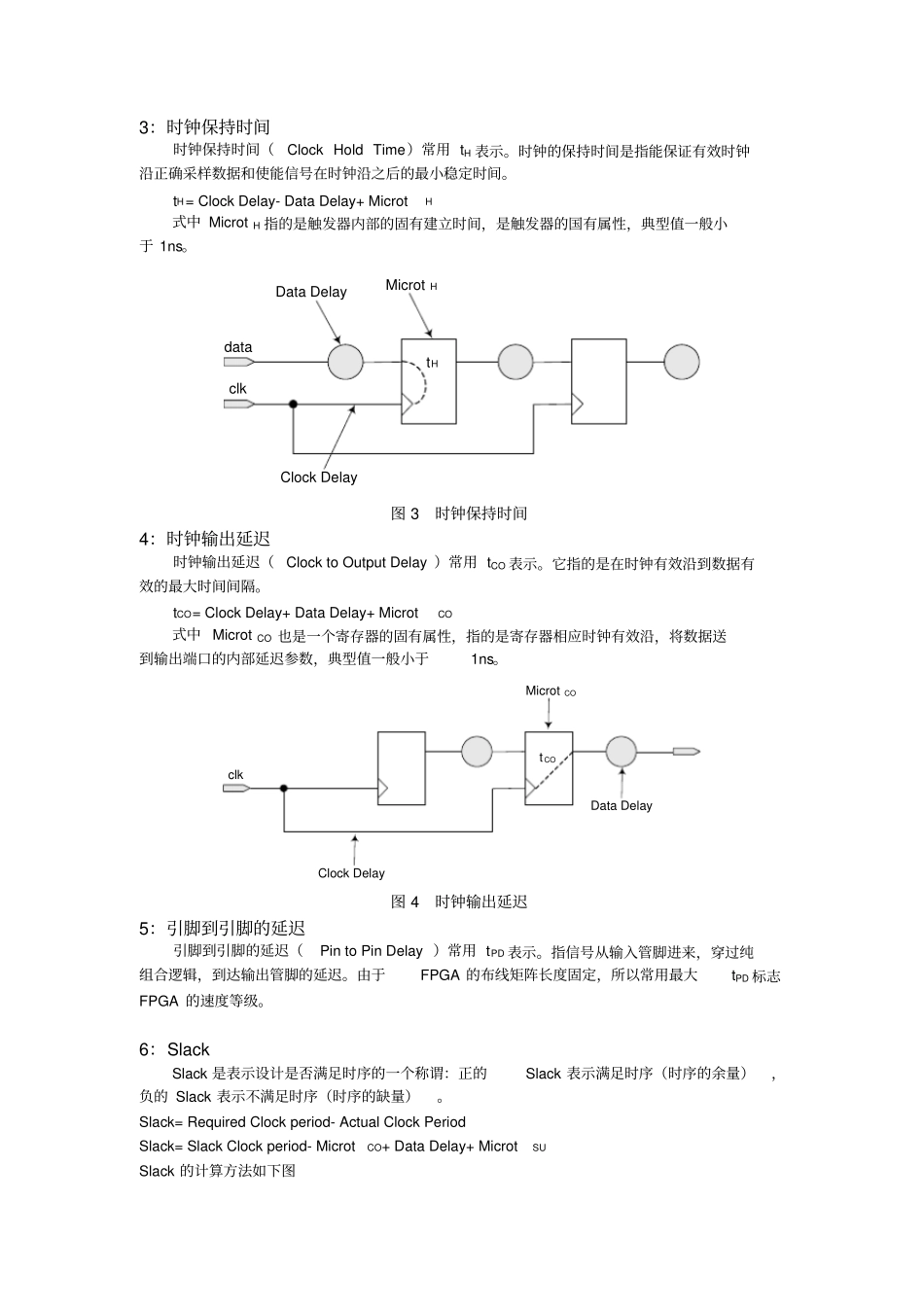

时钟和延迟1:周期与最高频率图 1 所示电路的最小时钟周期tCLK= Microt CO+t LOGIC +t NET+Microt SU-tCLK_SKEW 其中, tCLK_SKEW =tCD1-tCD2?tCLK 时钟的最小周期?Microt CO 寄存器固有的时钟输出延迟?tLOGIC 同步元件之间的组合逻辑延迟?tNET 线网延迟?Microt SU 寄存器固有的时钟建立时间?tCLK_SKEW 时钟偏斜QQSETCLRDQQSETCLRDtCD1tCD2tLOGICtNETMicrot COMicrot SU图 1 时钟周期的计算公式中最小时钟周期的倒数即最高频率,用f MAX 表示:fMAX=1/t CLK f MAX 能综合体现设计的时序性能,是最重要的时序指标之一。2:时钟建立时间时钟建立时间( Clock Setup Time )常用 tSU 表示。想要正确采样数据,就必须使数据和使能信号在有效时钟沿到达前就准备好。所谓时钟建立时间就是指时钟到达前,数据和使能信号已经准备好的最小时间间隔。图 2 所示电路的tSU 为;tSU= Data Delay-Clock Delay+MicrotSU 式中 Microt SU 指的是触发器内部的固有建立时间,是触发器的国有属性,典型值一般小于 1ns。Data DelayClock DelayMicrotSUtSUdataclk图 2 时钟建立时间3:时钟保持时间时钟保持时间(Clock Hold Time)常用 tH 表示。时钟的保持时间是指能保证有效时钟沿正确采样数据和使能信号在时钟沿之后的最小稳定时间。tH= Clock Delay- Data Delay+ MicrotH式中 Microt H 指的是触发器内部的固有建立时间,是触发器的国有属性,典型值一般小于 1ns。Data DelayClock DelayMicrot HtHdataclk图 3 时钟保持时间4:时钟输出延迟时钟输出延迟( Clock to Output Delay )常用 tCO 表示。它指的是在时钟有效沿到数据有效的最大时间间隔。tCO= Clock Delay+ Data Delay+ MicrotCO 式中 Microt CO 也是一个寄存器的固有属性,指的是寄存器相应时钟有效沿,将数据送到输出端口的内部延迟参数,典型值一般小于1ns。Clock DelayMicrot COclkData Delayt CO图 4 时钟输出延迟5:引脚到引脚的延迟引脚到引脚的延迟(Pin to Pin Delay )常用 tPD 表示。指信号从输入管脚进来,穿过纯组合逻辑,到达输出管脚的延迟。由于FPGA 的布线矩阵长度固定,所以常用最大tPD 标志FPGA 的速度等级。6:Slack Slack 是表示设计是否满足时序的一个称谓:正的Slack 表示满足时序(时序的余量),负的 Slack 表示不满足时序(时序的缺量)。Slack= Required Clock peri...