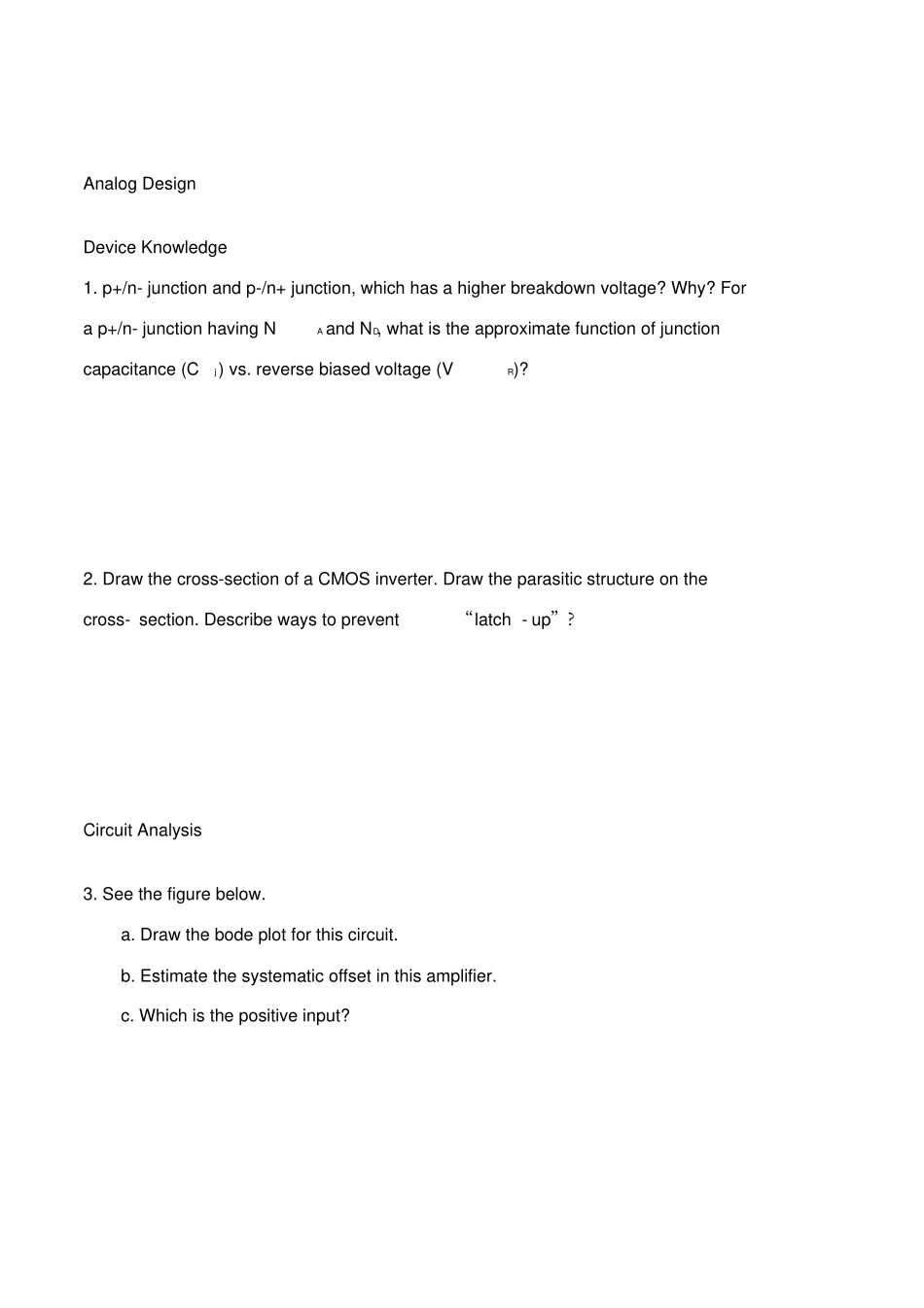

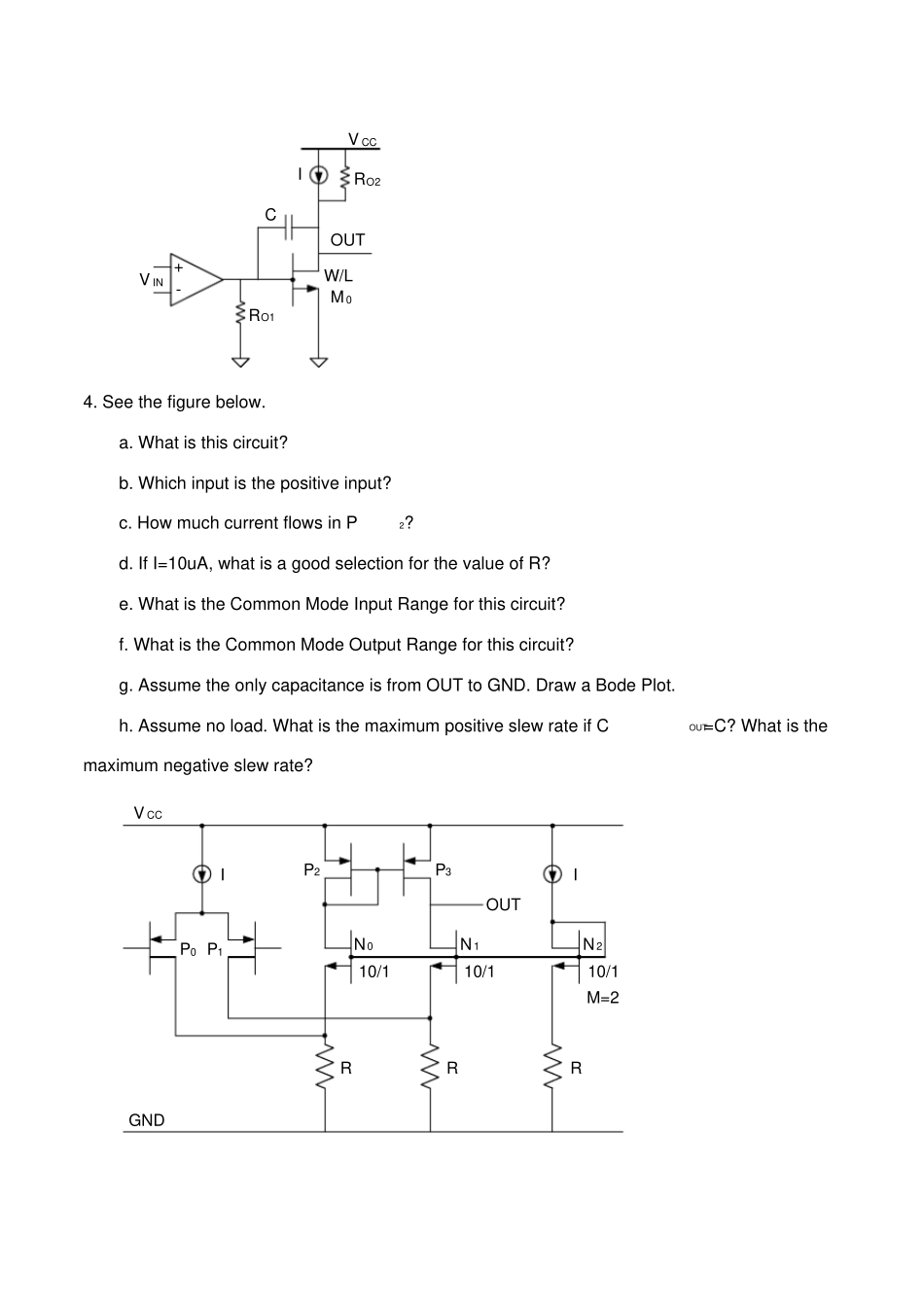

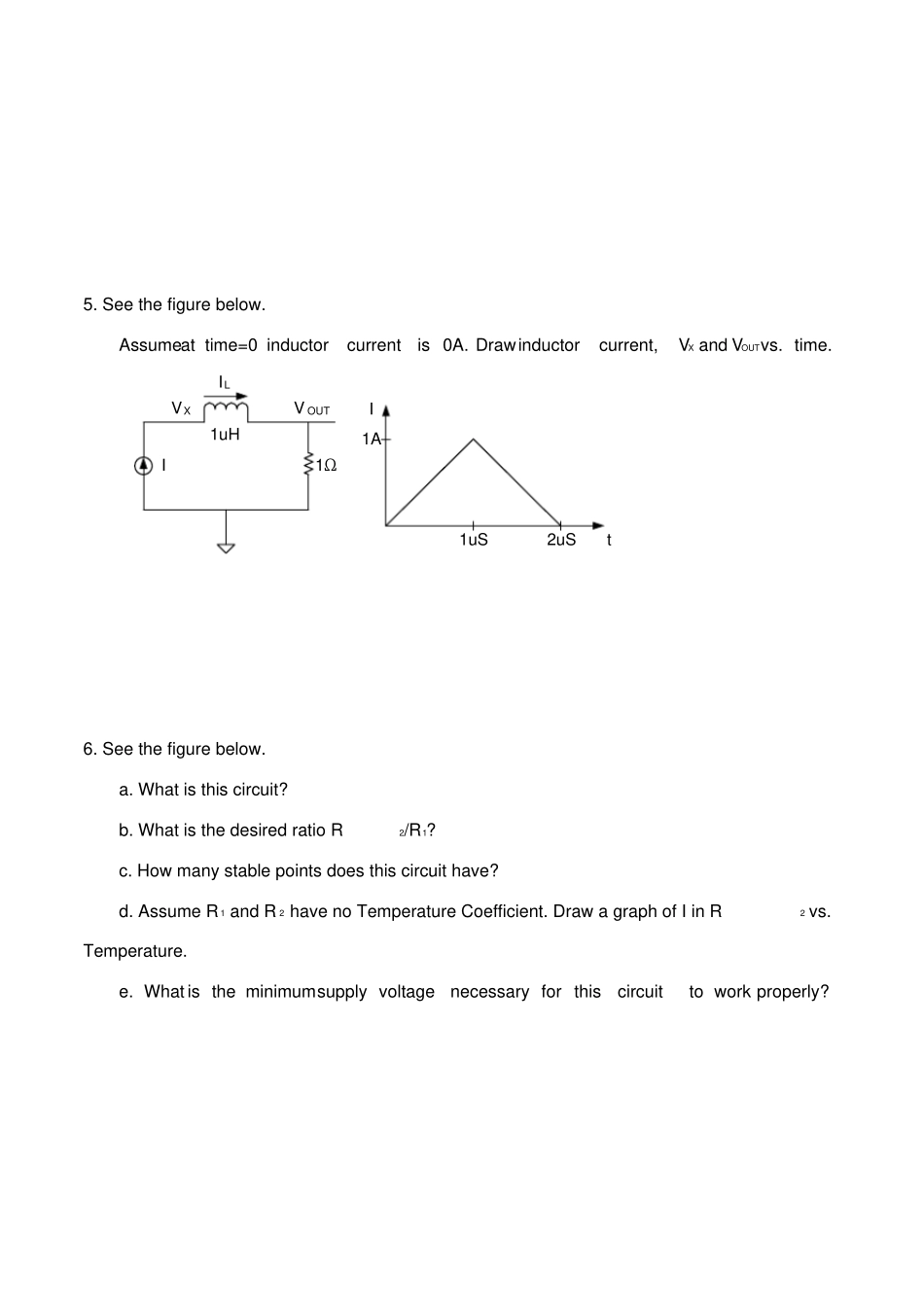

Analog DesignDevice Knowledge1. p+/n- junction and p-/n+ junction, which has a higher breakdown voltage? Why? For a p+/n- junction having NA and ND, what is the approximate function of junction capacitance (Cj) vs. reverse biased voltage (VR)?2. Draw the cross-section of a CMOS inverter. Draw the parasitic structure on the cross- section. Describe ways to prevent “latch - up”?Circuit Analysis3. See the figure below.a. Draw the bode plot for this circuit.b. Estimate the systematic offset in this amplifier.c. Which is the positive input?V CCRO2I+-V INOUTCRO1W/LM 04. See the figure below.a. What is this circuit?b. Which input is the positive input?c. How much current flows in P2?d. If I=10uA, what is a good selection for the value of R?e. What is the Common Mode Input Range for this circuit?f. What is the Common Mode Output Range for this circuit?g. Assume the only capacitance is from OUT to GND. Draw a Bode Plot.h. Assume no load. What is the maximum positive slew rate if COUT=C? What is the maximum negative slew rate?V CCIIP2P3N 0N 1N 2P1P0GNDRRR10/110/110/1M=2OUT5. See the figure below.Assume at time=0 inductor current is 0A. Draw inductor current, VX and VOUTvs. time.1ΩIL1uHV XV OUTI1A1uS2uStI6. See the figure below.a. What is this circuit?b. What is the desired ratio R2/R1?c. How many stable points does this circuit have?d. Assume R 1 and R 2 have no Temperature Coefficient. Draw a graph of I in R2 vs. Temperature.e. What is the minimum supply voltage necessary for this circuit to work properly?P0P1V OUTV CC10/110/18:1Q0Q1R1R27. See the figure below.a. Write the gain equation of each circuit.b. Assuming VO=0 at time 0. Sketch VO(t) for the given input signal.+-RRA+-CRB+-RCRCtV in8. Draw Bu...