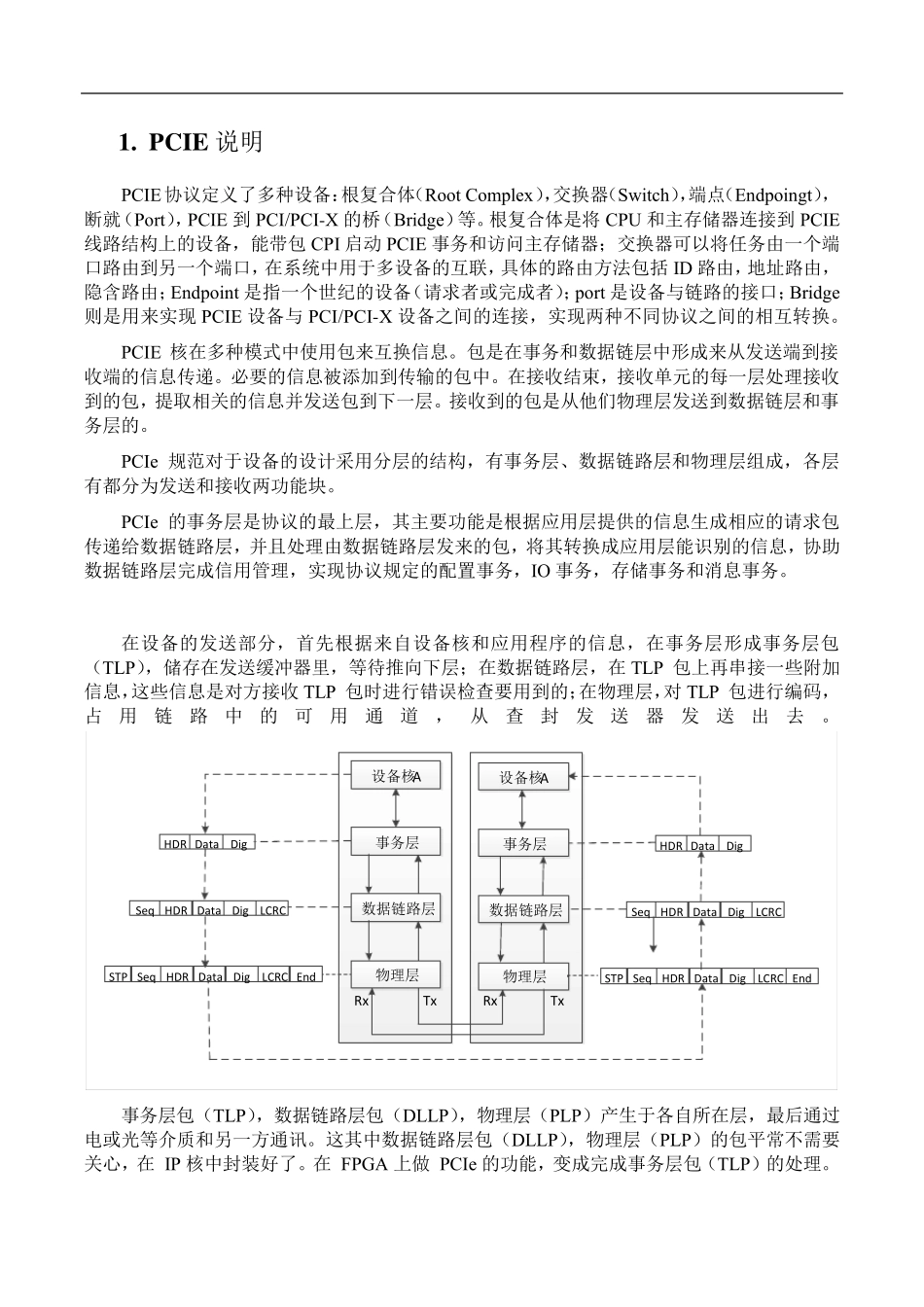

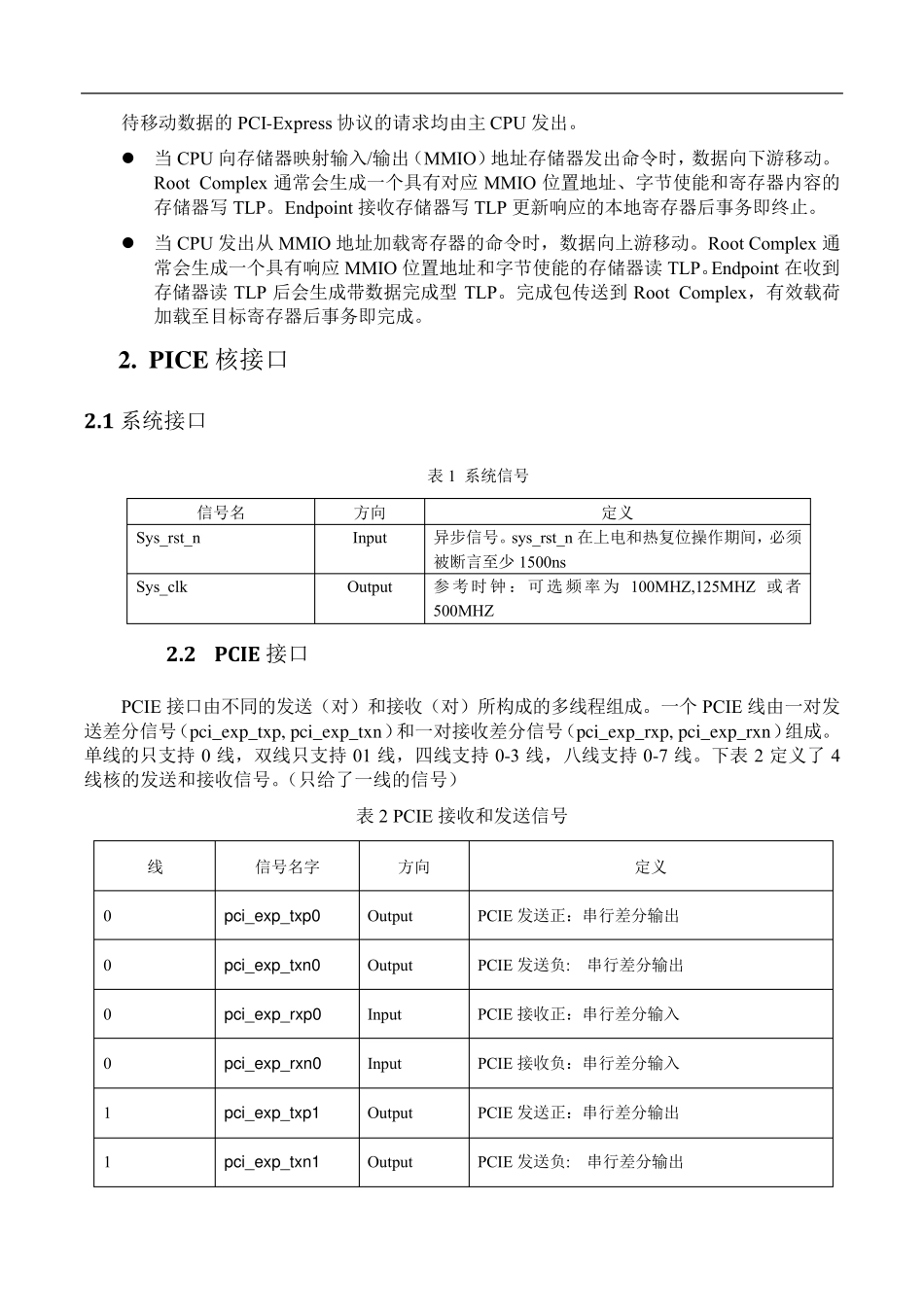

1. P CIE 说明 PCIE协议定义了多种设备:根复合体(Root Complex),交换器(Switch),端点(Endpoingt),断就(Port),PCIE 到 PCI/PCI-X 的桥(Bridge)等。根复合体是将 CPU 和主存储器连接到 PCIE线路结构上的设备,能带包 CPI 启动 PCIE 事务和访问主存储器;交换器可以将任务由一个端口路由到另一个端口,在系统中用于多设备的互联,具体的路由方法包括 ID 路由,地址路由,隐含路由;Endpoint 是指一个世纪的设备(请求者或完成者);port 是设备与链路的接口;Bridge则是用来实现 PCIE 设备与 PCI/PCI-X 设备之间的连接,实现两种不同协议之间的相互转换。 PCIE 核在多种模式中使用包来互换信息。包是在事务和数据链层中形成来从发送端到接收端的信息传递。必要的信息被添加到传输的包中。在接收结束,接收单元的每一层处理接收到的包,提取相关的信息并发送包到下一层。接收到的包是从他们物理层发送到数据链层和事务层的。 PCIe 规范对于设备的设计采用分层的结构,有事务层、数据链路层和物理层组成,各层有都分为发送和接收两功能块。 PCIe 的事务层是协议的最上层,其主要功能是根据应用层提供的信息生成相应的请求包传递给数据链路层,并且处理由数据链路层发来的包,将其转换成应用层能识别的信息,协助数据链路层完成信用管理,实现协议规定的配置事务,IO 事务,存储事务和消息事务。 在设备的发送部分,首先根据来自设备核和应用程序的信息,在事务层形成事务层包(TLP),储存在发送缓冲器里,等待推向下层;在数据链路层,在 TLP 包上再串接一些附加信息,这些信息是对方接收 TLP 包时进行错误检查要用到的;在物理层,对TLP 包进行编码,占用链路中的可用通道,从查封发送器发送出去。设备核A事务层数据链路层物理层设备核A事务层数据链路层物理层TxTxRxRxSTP Seq HDR DataDigLCRC EndSeq HDR DataDigLCRCHDR DataDigSTP Seq HDR DataDigLCRC EndSeq HDR DataDigLCRCHDR DataDig 事务层包(TLP),数据链路层包(DLLP),物理层(PLP)产生于各自所在层,最后通过电或光等介质和另一方通讯。这其中数据链路层包(DLLP),物理层(PLP)的包平常不需要关心,在 IP 核中封装好了。在 FPGA 上做 PCIe 的功能,变成完成事务层包(TLP)的处理。 待移动数据的PCI-Express 协议的请求均由主CPU 发出。 当CPU 向存储器映射输入/输出(MMIO)地址存储器发出命...