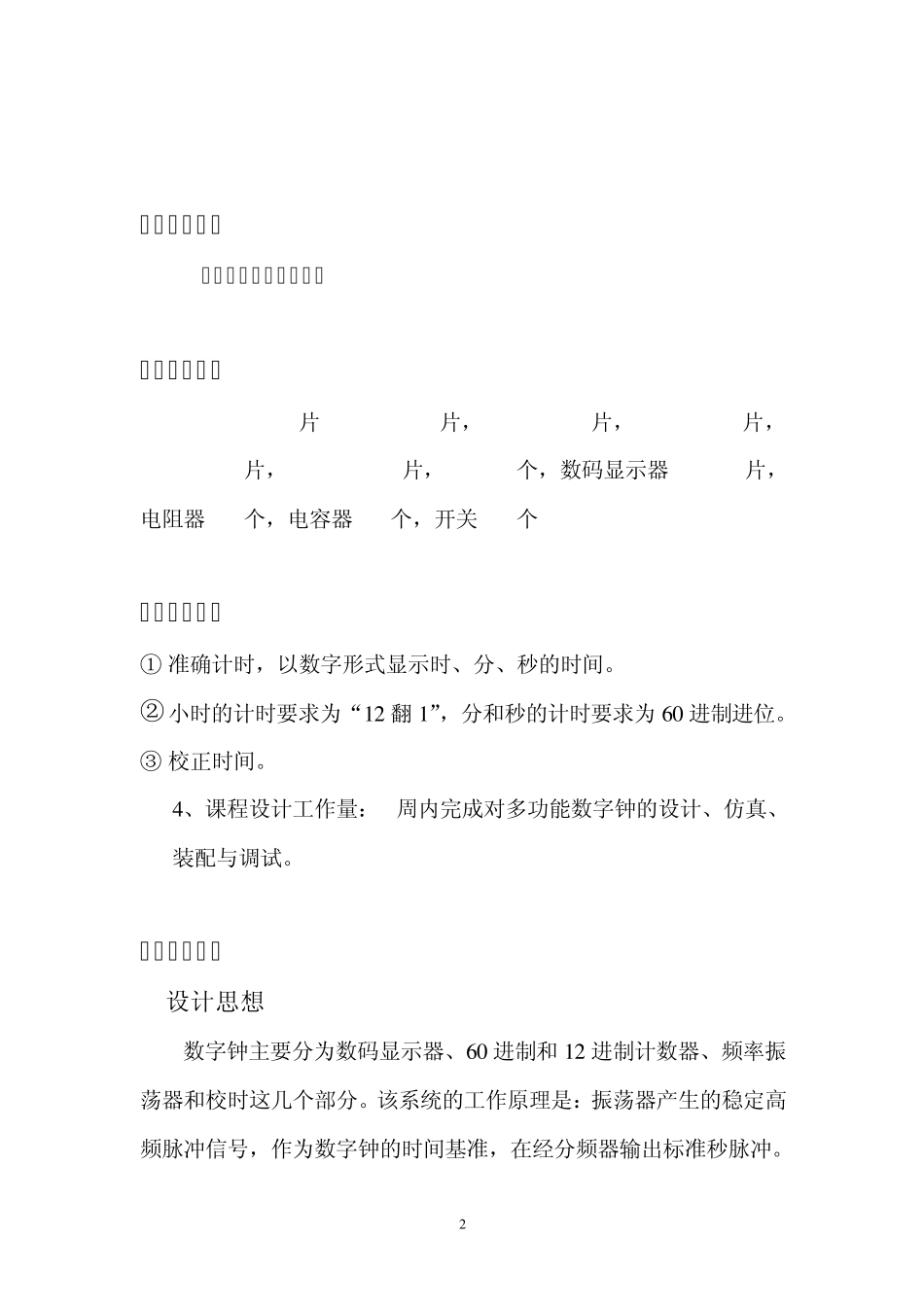

1 题 目:多功能数字钟设计 学校:广东石油化工学院 学院:机电工程学院 班级:装控 0 9 --2 姓名:黄亚冲 学号:1 6 2 一、设计任务 多功能数字钟电路设计 二、设计条件 74LS00 4片,74LS48 6片,74LS74 1片,74LS90 5片,74LS92 2片,74LS191 1片,555 1个,数码显示器202 6片,电阻器 6个,电容器 4个,开关 2个 三、设计要求 ① 准确计时,以数字形式显示时、分、秒的时间。 ② 小时的计时要求为“1 2 翻 1 ”,分和秒的计时要求为6 0 进制进位。 ③ 校正时间。 4 、课程设计工作量:1周内完成对多功能数字钟的设计、仿真、装配与调试。 四、设计内容 1.设计思想: 数字钟主要分为数码显示器、6 0 进制和 1 2 进制计数器、频率振荡器和校时这几个部分。该系统的工作原理是:振荡器产生的稳定高频脉冲信号,作为数字钟的时间基准,在经分频器输出标准秒脉冲。 3 秒计数器计满60 后向分计数器进位,分计数器计满60 后向小时计数器进位,小时计数器按照“12 翻 1”规律计数。计数器的输出经译码器送显示器。计时出现误差时可以用校时电路进行校时、校分、校秒。 图 1、多功能数字钟系统组成框图 2 .电路结构与原理图 (1)振荡器 振荡器可由晶振组成,也可以由 555 定时器组成。图 3 是由 555定时器构成的1KHZ的自激振荡器,其原理是0.7(2R3+R4+R5)C4=1ms,f=1/t=1KHZ。计时是 1HZ 的脉冲才是 1S 计一次数,所以需要分频才能得到 1HZ 的脉冲。 4 图2、晶体振荡器 图3、555 振荡器 (2)分频器的设计 分频器电路,是三个用十进制计数器 74LS90 串联而成的分频器,分频原理是在 74LS90 的输出端子中,从低位输入 10 个脉冲才从高位输出 1 个脉冲,这样一片 74LS90 就可以起十分频的作用,三个74LS90 串联就构成了千分频的电路,输出的便是 1HZ 的信号,从而达到目的。电路图见图4 图4、分频器 5 (3)小时计数器的设计——12 进制计数器 时计数器是一个“12 翻 1”的特殊进制计数器,即当数字钟运行到 12 时59 分 59 秒,秒的个位计数器再输入一个秒脉冲是,数字钟应自动显示为 01 时00 分 00 秒,实现日常生活中习惯用的计时规律。选用 74LS191 和 74LS74,电路图见图 5。 图 5、十二进制计数器 (4)分和秒的计数器——60 进制计数器: 分和秒计数器都是模数M=60 的计数器,其计数规律为 00—01—…58—59—00 ...选 7...