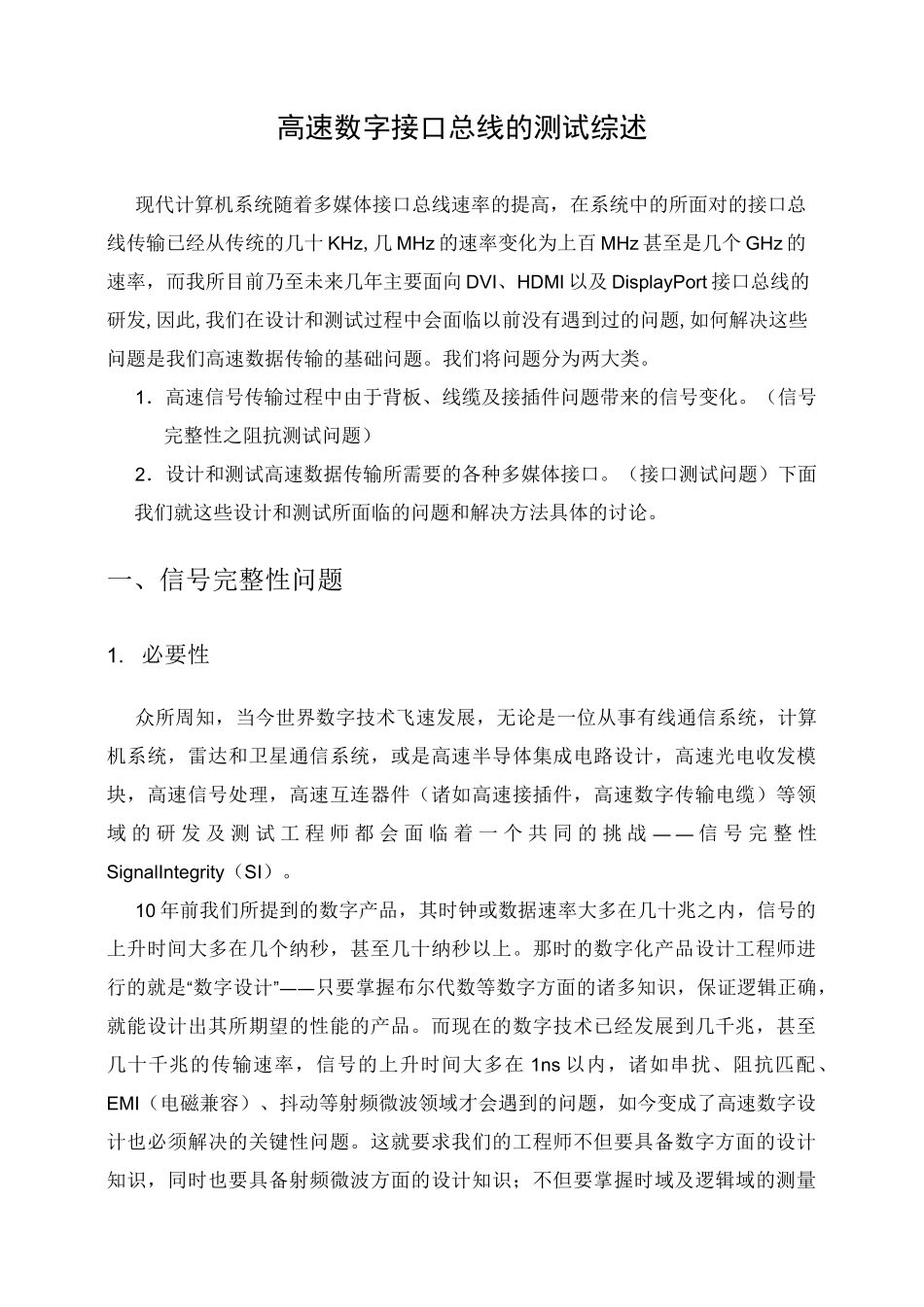

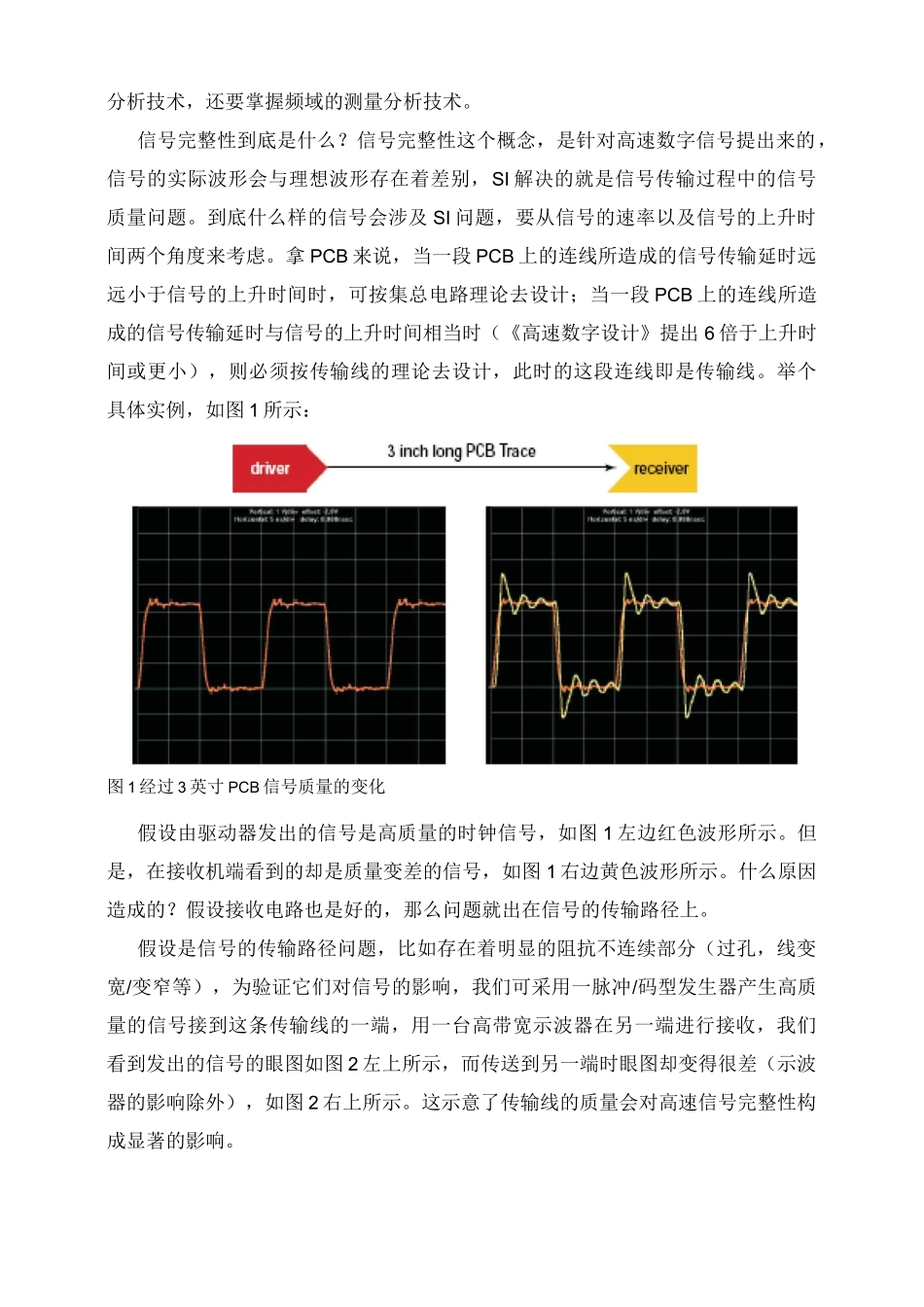

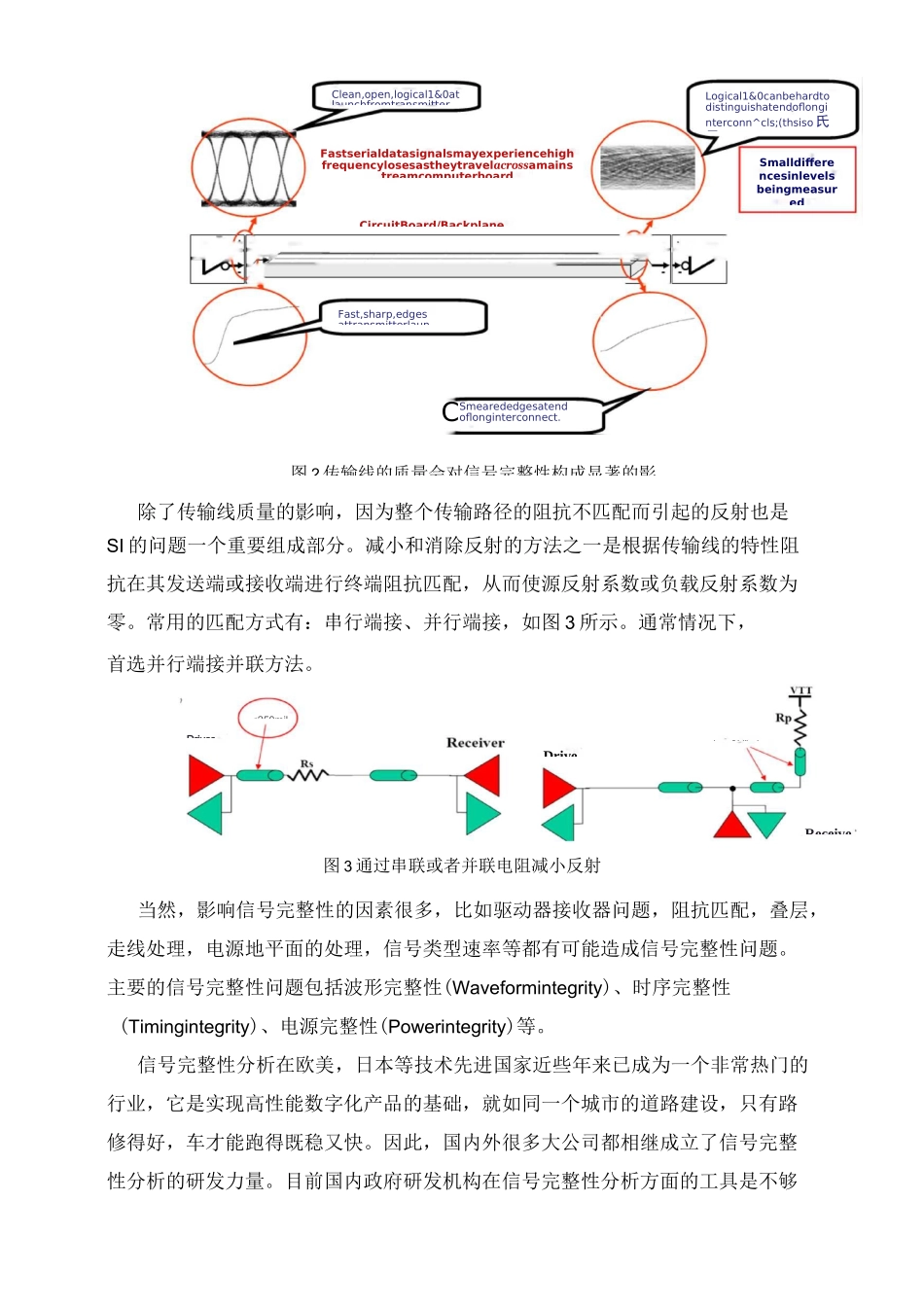

高速数字接口总线的测试综述现代计算机系统随着多媒体接口总线速率的提高,在系统中的所面对的接口总线传输已经从传统的几十 KHz,几 MHz 的速率变化为上百 MHz 甚至是几个 GHz 的速率,而我所目前乃至未来几年主要面向 DVI、HDMI 以及 DisplayPort 接口总线的研发,因此,我们在设计和测试过程中会面临以前没有遇到过的问题,如何解决这些问题是我们高速数据传输的基础问题。我们将问题分为两大类。1.高速信号传输过程中由于背板、线缆及接插件问题带来的信号变化。(信号完整性之阻抗测试问题)2.设计和测试高速数据传输所需要的各种多媒体接口。(接口测试问题)下面我们就这些设计和测试所面临的问题和解决方法具体的讨论。一、信号完整性问题1. 必要性众所周知,当今世界数字技术飞速发展,无论是一位从事有线通信系统,计算机系统,雷达和卫星通信系统,或是高速半导体集成电路设计,高速光电收发模块,高速信号处理,高速互连器件(诸如高速接插件,高速数字传输电缆)等领域 的 研 发 及 测 试 工 程 师 都 会 面 临 着 一 个 共 同 的 挑 战 — — 信 号 完 整 性SignalIntegrity(SI)。10 年前我们所提到的数字产品,其时钟或数据速率大多在几十兆之内,信号的上升时间大多在几个纳秒,甚至几十纳秒以上。那时的数字化产品设计工程师进行的就是“数字设计”――只要掌握布尔代数等数字方面的诸多知识,保证逻辑正确,就能设计出其所期望的性能的产品。而现在的数字技术已经发展到几千兆,甚至几十千兆的传输速率,信号的上升时间大多在 1ns 以内,诸如串扰、阻抗匹配、EMI(电磁兼容)、抖动等射频微波领域才会遇到的问题,如今变成了高速数字设计也必须解决的关键性问题。这就要求我们的工程师不但要具备数字方面的设计知识,同时也要具备射频微波方面的设计知识;不但要掌握时域及逻辑域的测量分析技术,还要掌握频域的测量分析技术。信号完整性到底是什么?信号完整性这个概念,是针对高速数字信号提出来的,信号的实际波形会与理想波形存在着差别,SI 解决的就是信号传输过程中的信号质量问题。到底什么样的信号会涉及 SI 问题,要从信号的速率以及信号的上升时间两个角度来考虑。拿 PCB 来说,当一段 PCB 上的连线所造成的信号传输延时远远小于信号的上升时间时,可按集总电路理论去设计;当一段 PCB 上的连线所造成的信号传输延时与信号的上升时间相当时(《高速数字设计》提...