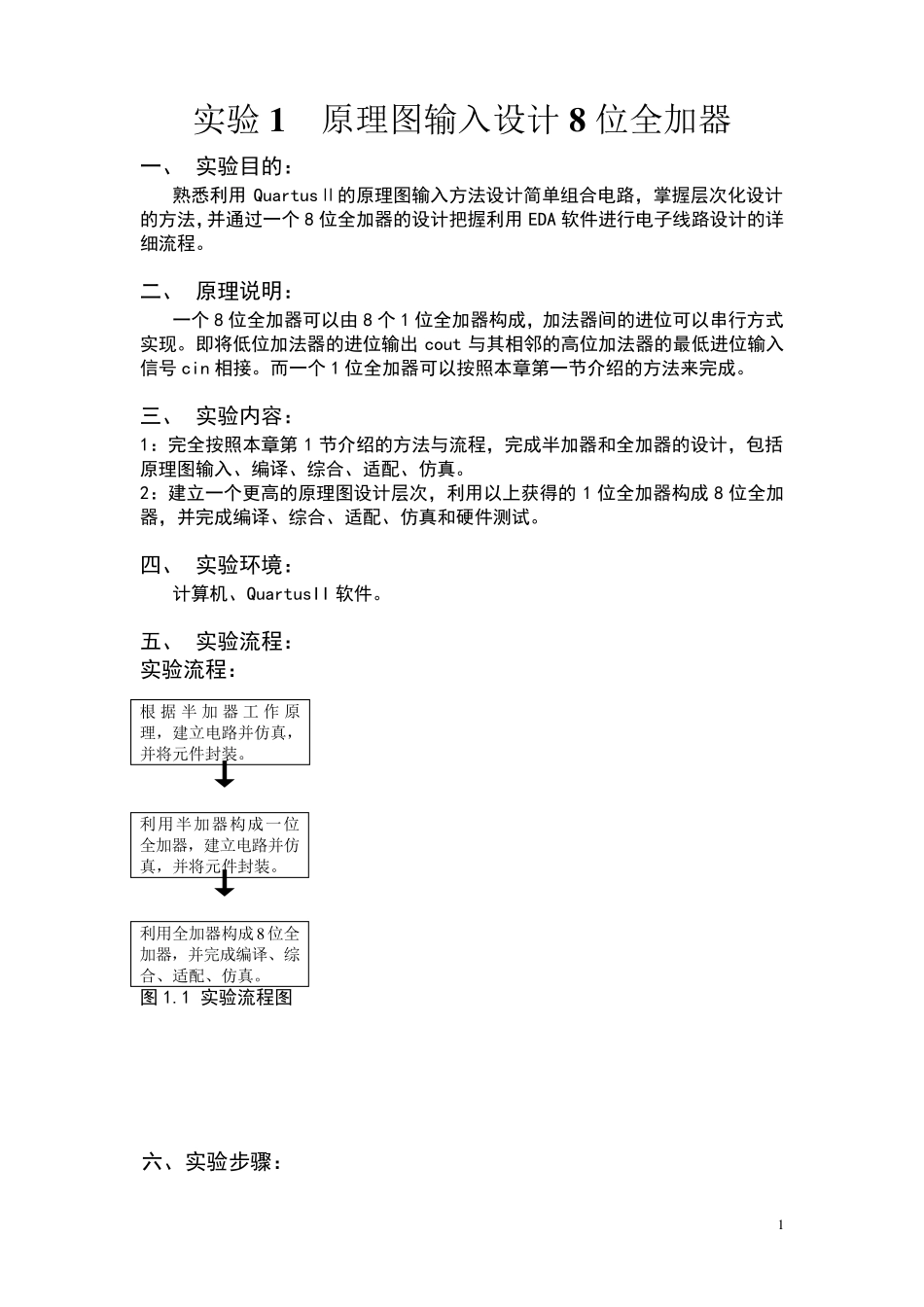

1 实验1 原理图输入设计8 位全加器 一、 实验目的: 熟悉利用QuartusⅡ的原理图输入方法设计简单组合电路,掌握层次化设计的方法,并通过一个 8 位全加器的设计把握利用EDA 软件进行电子线路设计的详细流程。 二、 原理说明: 一个 8 位全加器可以由 8 个 1 位全加器构成,加法器间的进位可以串行方式实现。即将低位加法器的进位输出 cout 与其相邻的高位加法器的最低进位输入信号 cin 相接。而一个 1 位全加器可以按照本章第一节介绍的方法来完成。 三、 实验内容: 1:完全按照本章第 1 节介绍的方法与流程,完成半加器和全加器的设计,包括原理图输入、编译、综合、适配、仿真。 2:建立一个更高的原理图设计层次,利用以上获得的1 位全加器构成 8 位全加器,并完成编译、综合、适配、仿真和硬件测试。 四、 实验环境: 计算机、QuartusII 软件。 五、 实验流程: 实验流程: ↓ 利用半加器构成一位全加器,建立电路并仿真,并将元件封装。 ↓ 利用全加器构成8 位全加器,并完成编译、综合、适配、仿真。 图 1.1 实验流程图 六、实验步骤: 根 据 半加器工 作 原理,建立电路并仿真,并将元件封装。 21.根据半加器工作原理建立电路并仿真,并将元件打包。 (1)半加器原理图: 图 1.2 半加器原理图 (2)综合报告: 图 1.3 综合报告: (3)功能仿真波形图 4: 图 1.4 功能仿真波形图 时序仿真波形图: 3 图1 .5 时序仿真波形图 仿真结果分析:sou t 为和信号,当a=1,b=0 或a=0,b=1 时,和信号sou t 为1,否则为0.当a=b=1 时,产生进位信号,及cou t=1。 (4 )时序仿真的延时情况: 图1.6 时序仿真的延时情况 (5 )封装元件: 图1.7 元件封装图 2 . 利用半加器构成一位全加器,建立电路并仿真,并将元件封装。 (1 )全加器原理图如图: 图2 .1 全加器原理图 (2 )综合报告: 4 图2 .2 综合报告 (3 )功能仿真波形图: 图2 .3 功能仿真波形图 时序仿真波形图: 图2 .4 时序仿真波形图 仿真结果分析:cin 为来自低位的进位,su m=a or b or cin,即:当a,b,cin 中有一位为高电平‘1’或者三位同时高电平为‘1’,则 su m=1,否则 su m=0;当a,b,cin 有两位或者三位同为高电平‘1’时,产生进位信号 cou t=‘1’。 (4 )时序仿真的延时情况: 图2 .5 时序仿真的延时情况 (5 )封装元件: 5 图2...