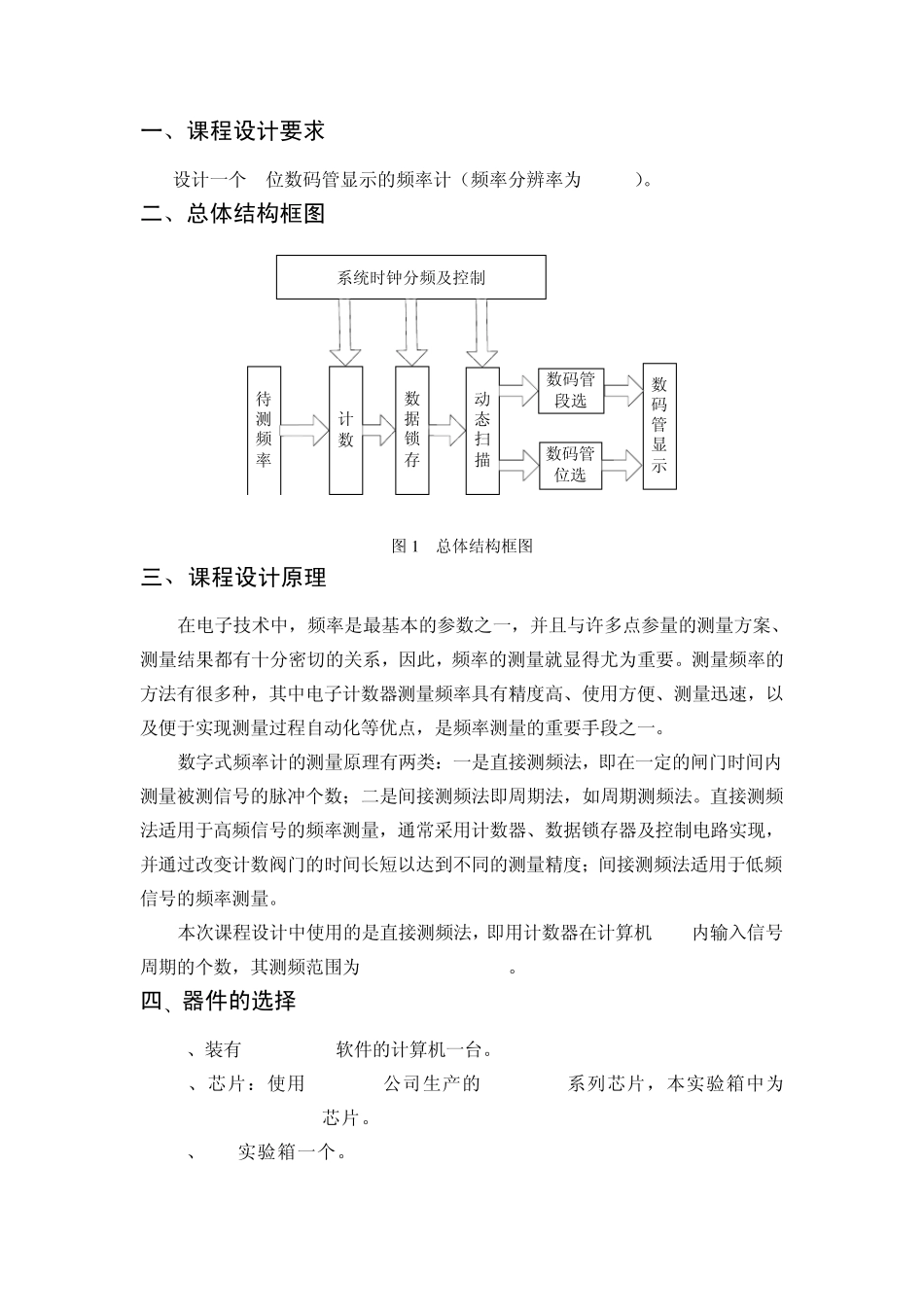

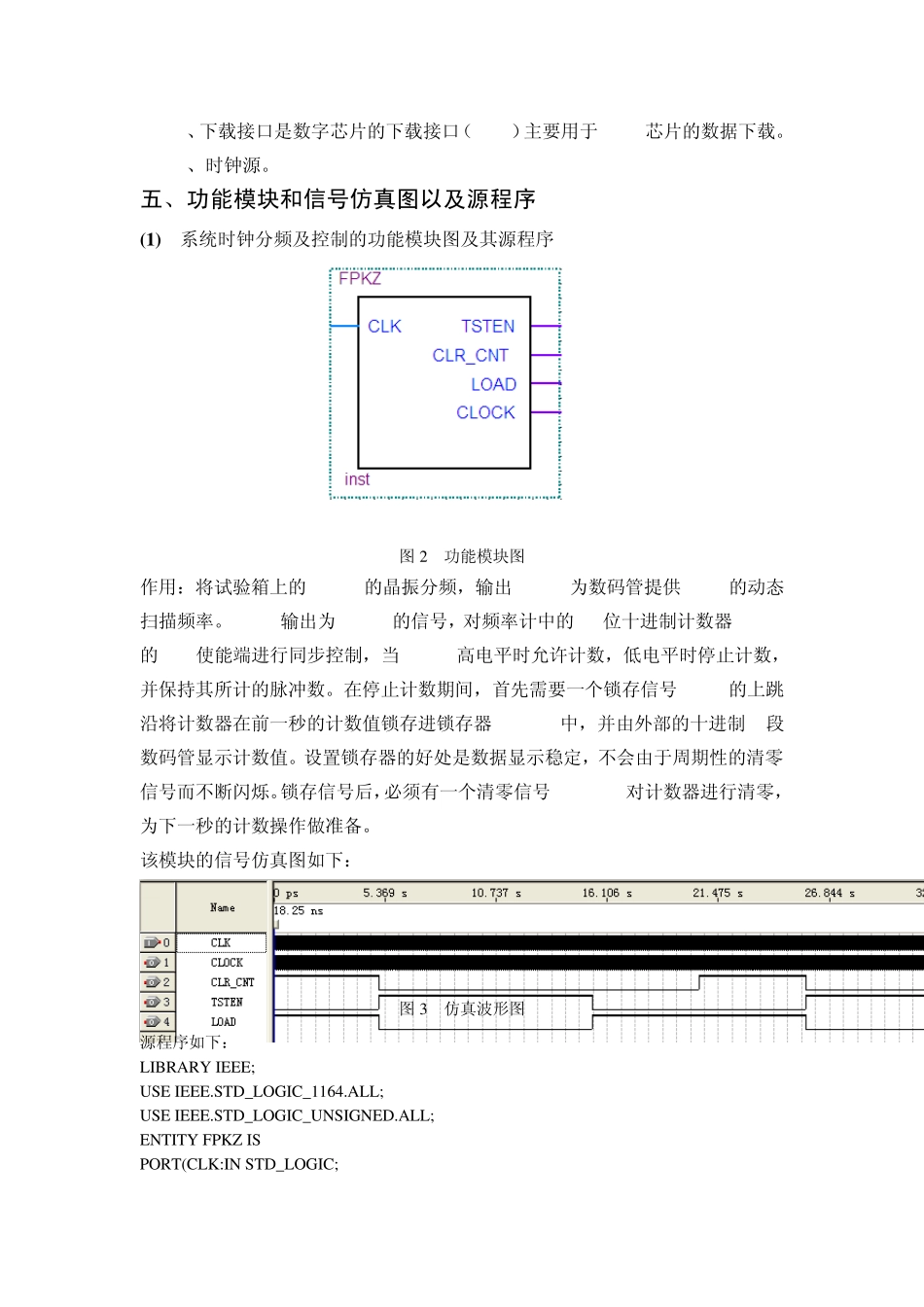

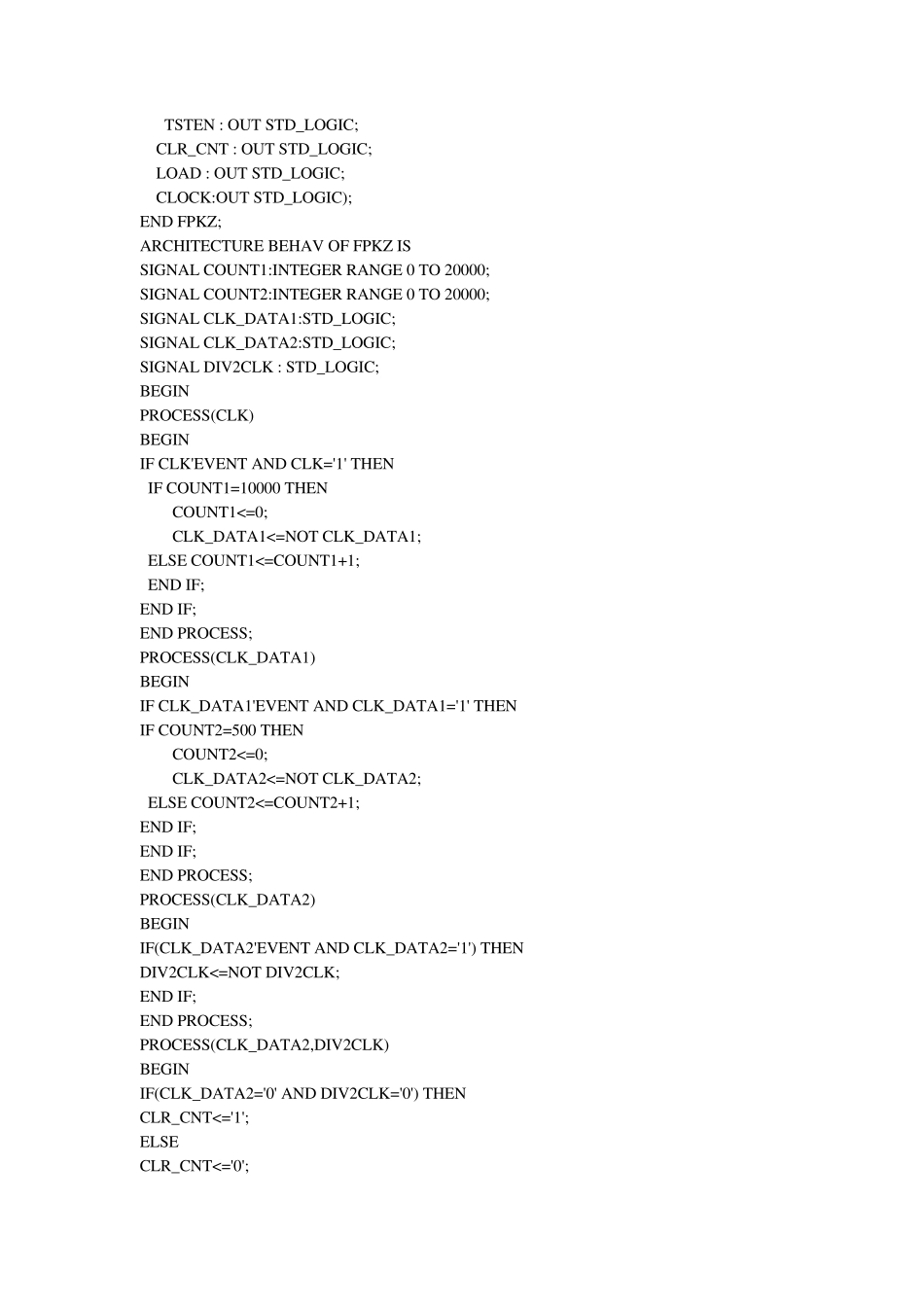

一、课程设计要求 设计一个8位数码管显示的频率计(频率分辨率为0.1Hz)。 二、总体结构框图 系统时钟分频及控制计数数据锁存动态扫描数码管段选待测频率数码管位选数码管显示 图1 总体结构框图 三、课程设计原理 在电子技术中,频率是最基本的参数之一,并且与许多点参量的测量方案、测量结果都有十分密切的关系,因此,频率的测量就显得尤为重要。测量频率的方法有很多种,其中电子计数器测量频率具有精度高、使用方便、测量迅速,以及便于实现测量过程自动化等优点,是频率测量的重要手段之一。 数字式频率计的测量原理有两类:一是直接测频法,即在一定的闸门时间内测量被测信号的脉冲个数;二是间接测频法即周期法,如周期测频法。直接测频法适用于高频信号的频率测量,通常采用计数器、数据锁存器及控制电路实现,并通过改变计数阀门的时间长短以达到不同的测量精度;间接测频法适用于低频信号的频率测量。 本次课程设计中使用的是直接测频法,即用计数器在计算机 10s内输入信号周期的个数,其测频范围为0Hz-9999999.9Hz。 四、器件的选择 1、装有 QuartusII软件的计算机一台。 2、芯片:使用 altera公司生产的Cyclone系列芯片,本实验箱中为EP1C8Q208C8N芯片。 3、EDA实验箱一个。 4、下载接口是数字芯片的下载接口(JTAG)主要用于 FPGA芯片的数据下载。 5、时钟源。 五、功能模块和信号仿真图以及源程序 (1 ) 系统时钟分频及控制的功能模块图及其源程序 图 2 功能模块图 作用:将试验箱上的 20MHz的晶振分频,输出 CLOCK为数码管提供 1kHz的动态扫描频率。TSTEN输出为 0.05s的信号,对频率计中的 32位十进制计数器 CNT10的 ENA使能端进行同步控制,当 TSTEN高电平时允许计数,低电平时停止计数,并保持其所计的脉冲数。在停止计数期间,首先需要一个锁存信号 LOAD的上跳沿将计数器在前一秒的计数值锁存进锁存器 REG32B中,并由外部的十进制 7段数码管显示计数值。设置锁存器的好处是数据显示稳定,不会由于周期性的清零信号而不断闪烁。锁存信号后,必须有一个清零信号 CLR_CNT对计数器进行清零,为下一秒的计数操作做准备。 该模块的信号仿真图如下: 图 3 仿真波形图 源程序如下: LIBRARY IEEE; USE IEEE.STD_LOGIC_1164.ALL; USE IEEE.STD_LOGIC_UNSIGNED.ALL; ENTITY FPKZ IS PORT(CLK:IN STD_LOGIC; TSTEN : OUT STD_LOGIC; CLR_CNT : OUT STD_LOGIC; LOAD : OU...