8 点流水线型FFT 的Verilog HDL 实现 梁志明 华南理工大学 calaok@sohu

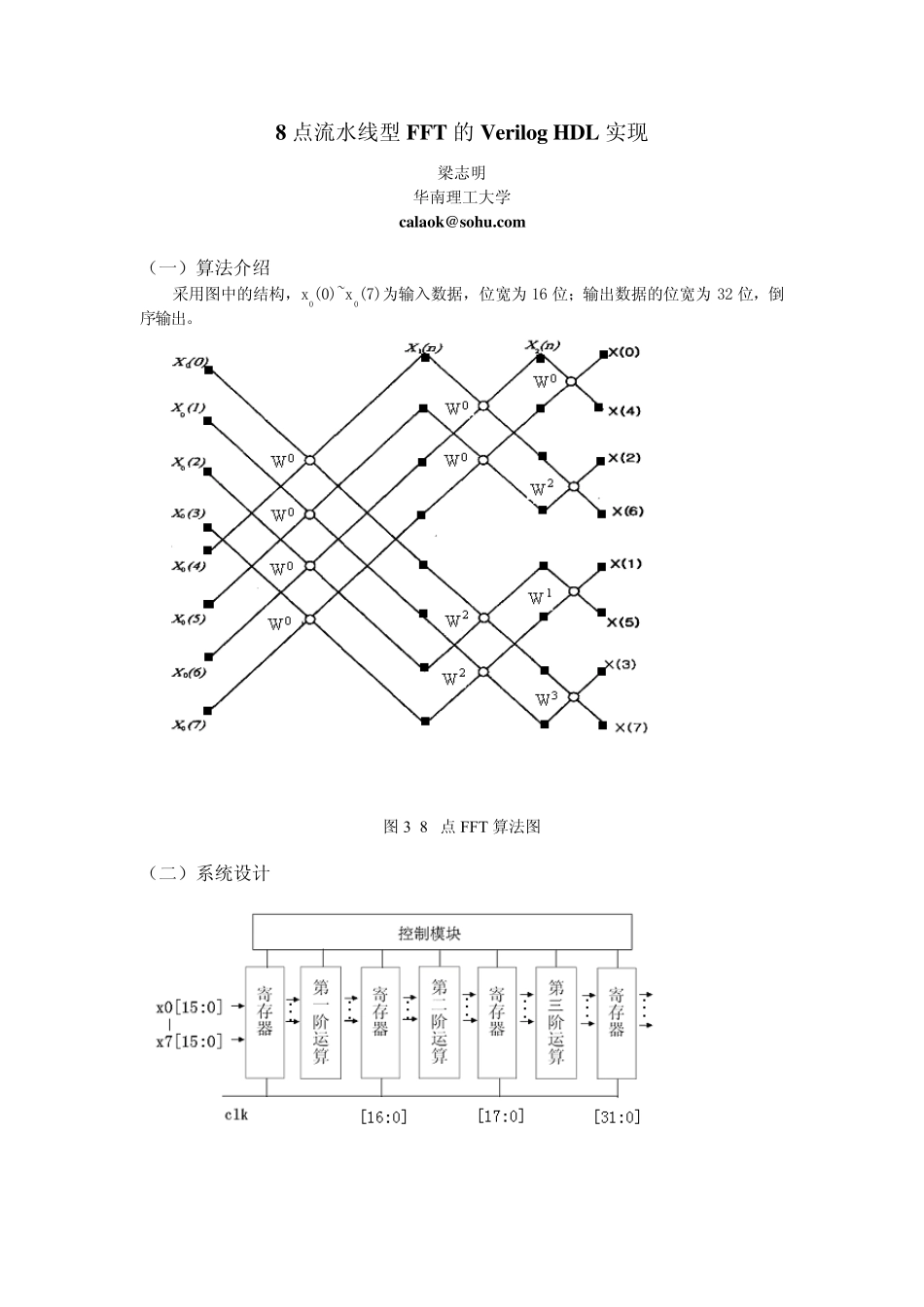

com (一)算法介绍 采用图中的结构,x0(0)~x0(7)为输入数据,位宽为16 位;输出数据的位宽为32 位,倒序输出

图3 8 点FFT 算法图 (二)系统设计 图4 系统总框图 1、系统总框图如图4 所示,总共包括一下几个模块: 1. 运算模块

对应三阶运算,共采用三个运算子模块: 第一阶运算模块:对应蝶形算子只有 W0 (W0=1), 第二阶运算模块:对应蝶形算子有 W0 、W2(W2=-j), 第三阶运算模块:对应蝶形算子有 W0 、W1 、W2 、W3

2. 控制模块 针对各阶运算,控制模块也可分为三个子模快: 第一阶控制模块; 第二阶控制模块; 第三阶控制模块

2、各个运算模块分析

1.第一阶运算模块: 模块功能:完成 FFT 第一阶蝶形运算

模块设计: 此时蝶形算子只有 W0,故蝶形运算结果为 C=A+B,D=A-B

因此,只需要对输入数据做加减法即可

考虑资源复用,这里定义一个 16 位的有符号数加法器和减法器,每次运算直接调用即可

2.第二阶运算模块 模块功能:完成 FFT 第二阶蝶形运算

模块设计: 第二阶运算有蝶形算子 W0 、W2

对于 W2 蝶形运算结果为 C=A+jB,D=A-jB,因此,只需另运算结果实部为A,虚部为+ /-B 即可

对于 W0 算子,这里定义了一个17 位有符号数加法器和减法器处理

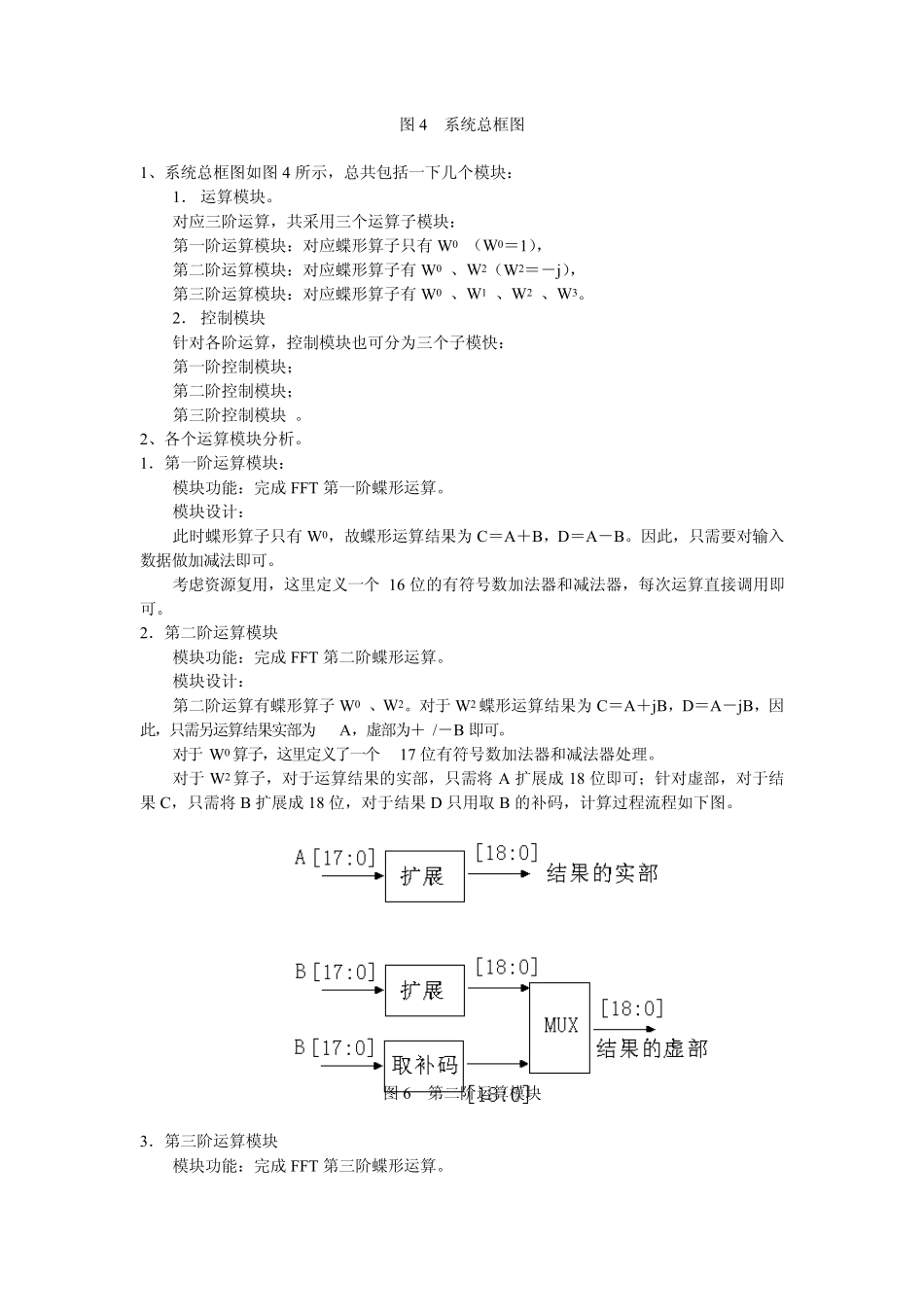

对于 W2 算子,对于运算结果的实部,只需将 A 扩展成 18 位即可;针对虚部,对于结果 C,只需将 B 扩展成 18 位,对于结果 D 只用取 B 的补码,计算过程流程如下图

图6 第二阶运算模块 3.第三阶运算模块 模块功能:完成 FFT 第三阶蝶形运算

模块设计: 第三阶运算模块:对应蝶形算子有W0 、W1