Allegro PCB 设计中的约束管理 本章主要介绍一下约束管理器的使用,约束管理器贯穿于原理图设计、PCB设计、仿真分析设计,这里主要讲述在 PCB Editor 中如何使用约束管理器来对信号进行约束设置

一、约束管理器概述 约束管理器是贯穿于整个 PCB 设计平台的一个对信号约束的工具,在整个项目的开发过程中,起着桥梁的作用

我们可以在原理图设计阶段在约束管理器中设定约束来指导 PCB 设计;也可以在使用仿真分析工具仿真后,将仿真分析的拓扑添加到约束管理器中从而来驱动布局、布线

约束管理器是以表格形式为基础的工作表形式,所以其操作简单、运用灵活

它将印制电路板所有的网名以表格形式显示,不仅使设计者对网名一目了然且更加方便地对信号设定不同的规则

对不同的规则如相对长度规则、总长度规则、曼哈顿长度规则等分了不同的栏显示以方便大家的规则设定

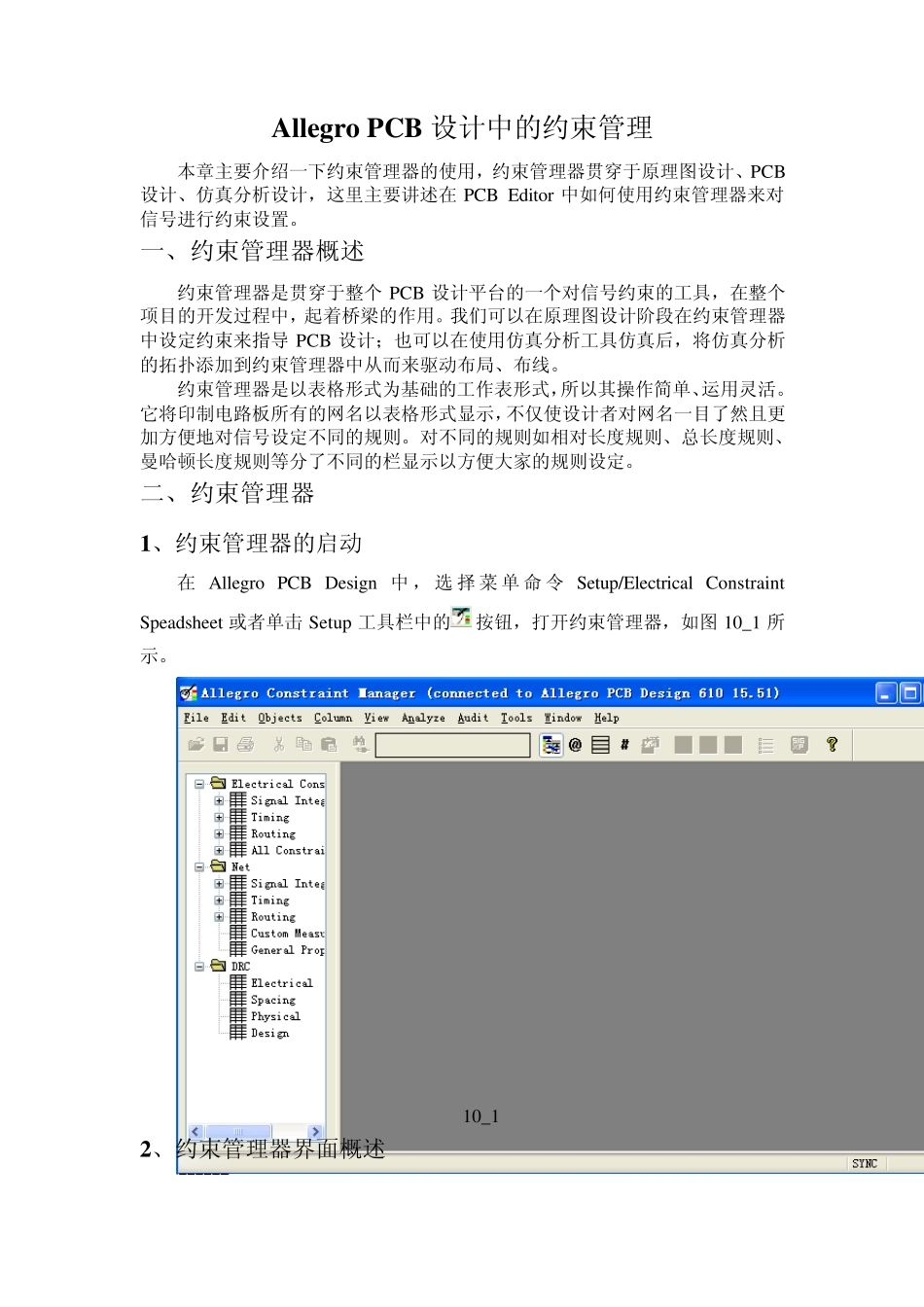

二、约束管理器 1、约束管理器的启动 在 Allegro PCB Design 中,选 择 菜 单 命 令 Setu p/Electrical Constraint Speadsheet 或者单击 Setu p 工具栏中的按钮,打开约束管理器,如图10_1 所示

10_1 2、约束管理器界面概述 1)菜单栏 约束管理器的菜单栏包括:File、Edit、Objects、Column、View、Analyze、Audit、Tools、Window 及Help

2)Electrical Constraint Set 栏 此栏主要是对电气规则来设定约束,包括:Signal Intergrity(信号完整性设置规则)、Timing(时序规则设置)、Routing(布线设置)、All Constraint(所有的约束管理)

3)Net 栏 Net 栏主要对指定的网络来设置不同的约束规则,包括Signal Intergrity(信号完整性