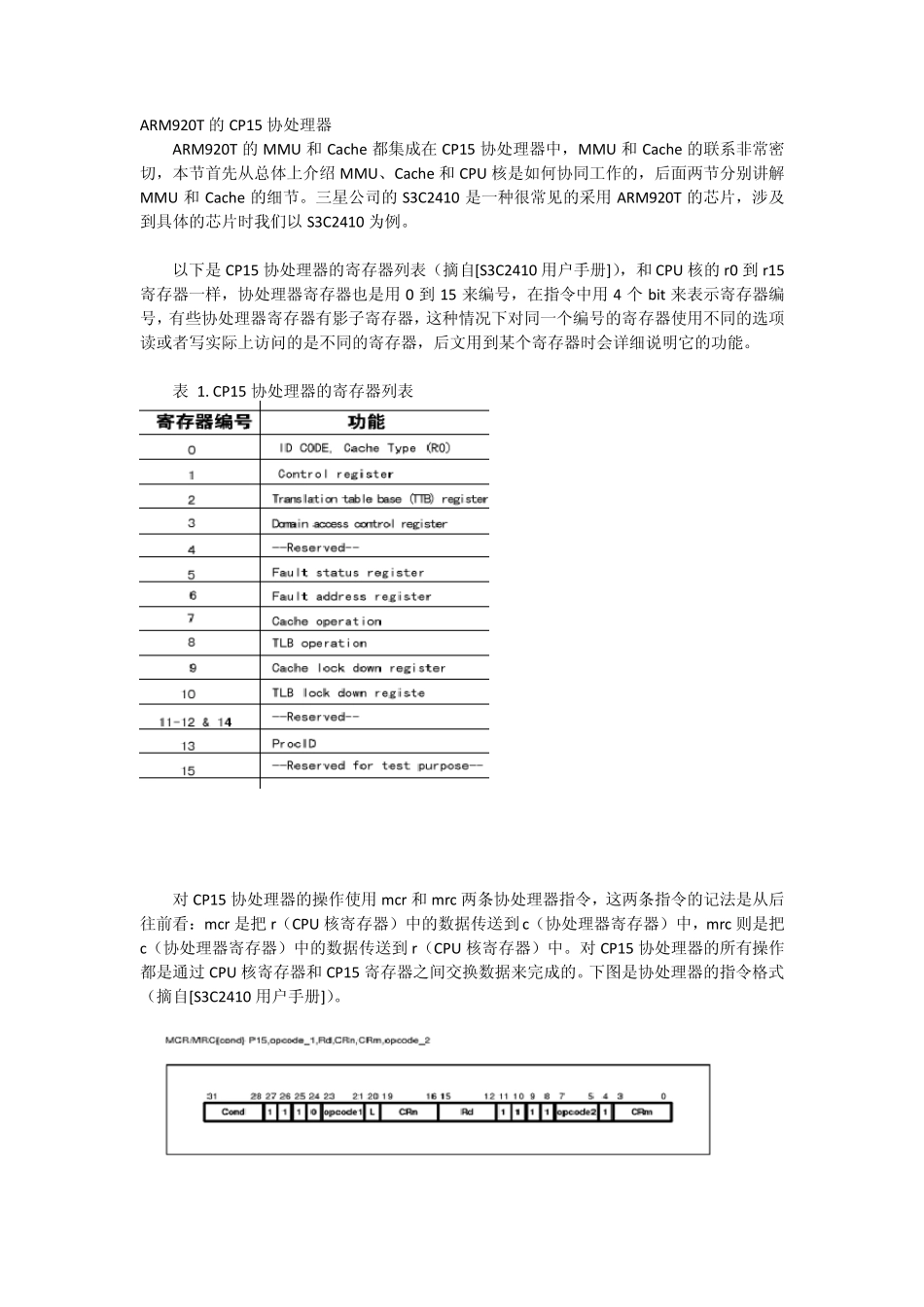

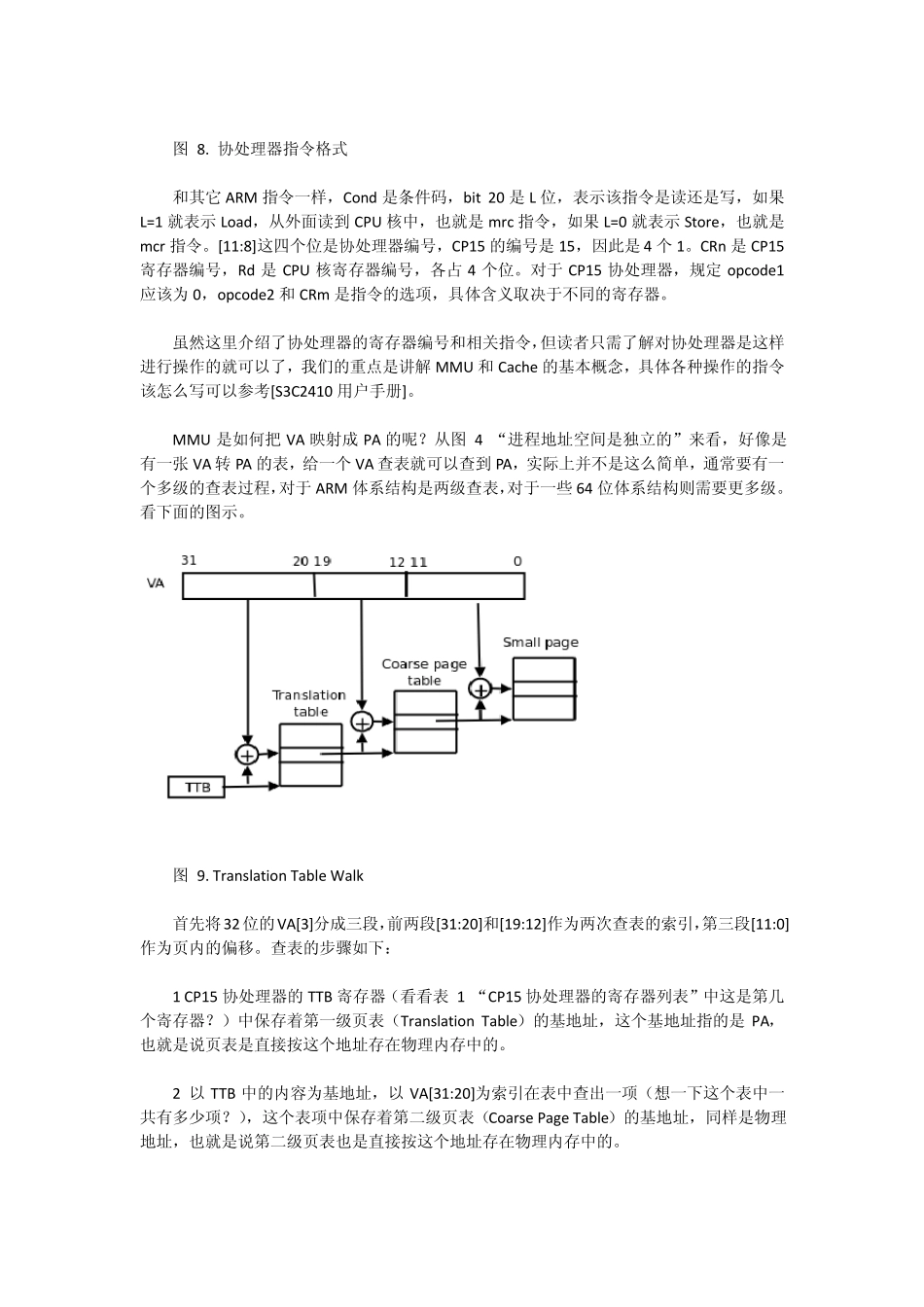

ARM920T 的CP15 协处理器 ARM920T 的MMU 和Cache 都集成在CP15 协处理器中,MMU 和Cache 的联系非常密切,本节首先从总体上介绍MMU、Cache 和CPU 核是如何协同工作的,后面两节分别讲解MMU 和Cache 的细节。三星公司的S3C2410 是一种很常见的采用 ARM920T 的芯片,涉及到具体的芯片时我们以 S3C2410 为例。 以下是 CP15 协处理器的寄存器列表(摘自[S3C2410 用户手册]),和CPU 核的r0 到 r15寄存器一样,协处理器寄存器也是用 0 到 15 来编号,在指令中用 4 个 bit 来表示寄存器编号,有些协处理器寄存器有影子寄存器,这种情况下对同一个编号的寄存器使用不同的选项读或者写实际上访问的是不同的寄存器,后文用到某个寄存器时会详细说明它的功能。 表 1. CP15 协处理器的寄存器列表 对 CP15 协处理器的操作使用 mcr 和mrc 两条协处理器指令,这两条指令的记法是从后往前看:mcr 是把 r(CPU 核寄存器)中的数据传送到 c(协处理器寄存器)中,mrc 则是把c(协处理器寄存器)中的数据传送到 r(CPU 核寄存器)中。对 CP15 协处理器的所有操作都是通过 CPU 核寄存器和CP15 寄存器之间交换数据来完成的。下图是协处理器的指令格式(摘自[S3C2410 用户手册])。 图 8. 协处理器指令格式 和其它ARM 指令一样,Cond 是条件码,bit 20 是L 位,表示该指令是读还是写,如果L=1 就表示Load,从外面读到CPU 核中,也就是mrc 指令,如果L=0 就表示Store,也就是mcr 指令。[11:8]这四个位是协处理器编号,CP15 的编号是15,因此是4 个1。CRn 是CP15寄存器编号,Rd 是CPU 核寄存器编号,各占4 个位。对于CP15 协处理器,规定opcode1应该为0,opcode2 和CRm 是指令的选项,具体含义取决于不同的寄存器。 虽然这里介绍了协处理器的寄存器编号和相关指令,但读者只需了解对协处理器是这样进行操作的就可以了,我们的重点是讲解MMU 和Cache 的基本概念,具体各种操作的指令该怎么写可以参考[S3C2410 用户手册]。 MMU 是如何把VA 映射成PA 的呢?从图 4 “进程地址空间是独立的”来看,好像是有一张 VA 转 PA 的表,给一个VA 查表就可以查到PA,实际上并不是这么简单,通常要有一个多级的查表过程,对于ARM 体系结构是两级查表,对于一些 64 位体系结构则需要更多级。看下面的图示。 图 9. Translation Table Walk 首先将32位的VA[3]分成三段,前两段[31:...