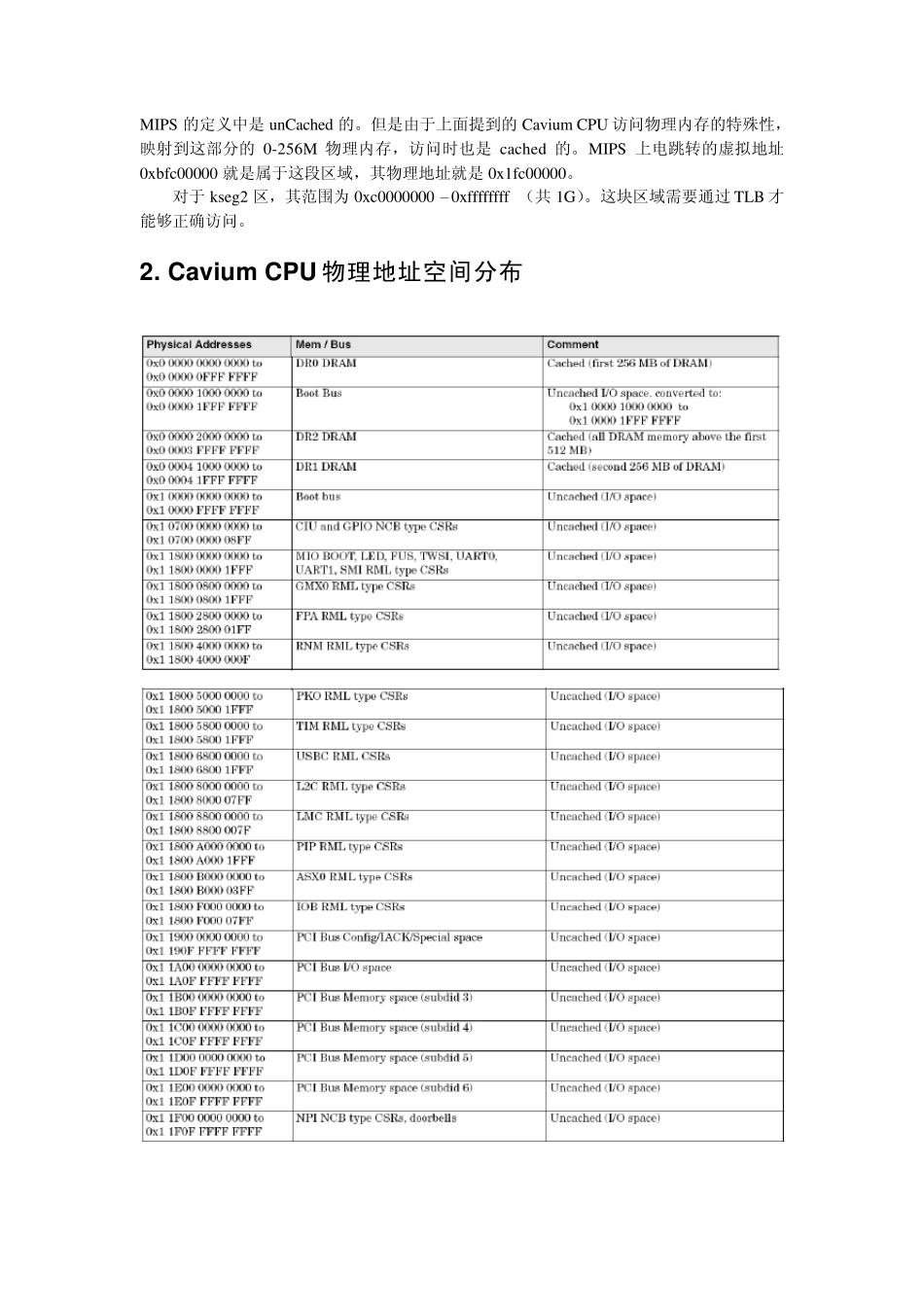

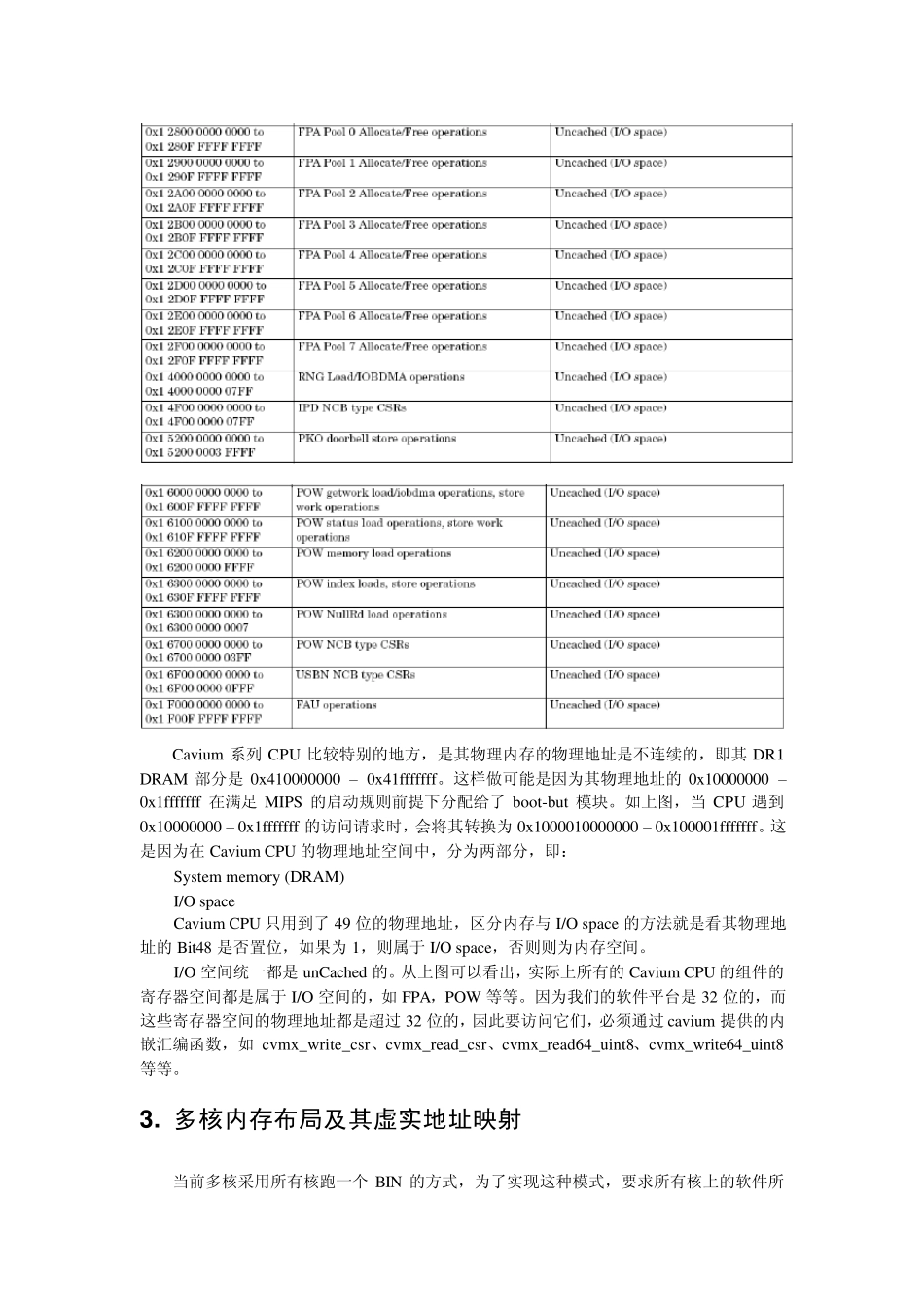

Cavium 多核系统地址空间布局及启动 引言 作为使用MIPS 内核的CPU 芯片,Cavium 系列CPU 具有两个地址空间,即虚拟地址空间和物理地址空间。在MIPS 系统中,软件所见到的都是虚拟地址,其与物理地址的联系是通过内核中的TLB 以及ERL 位共同决定。 1 . 虚拟地址 Cavium 系列CPU 在采用32 位寻址模式时,具有标准的一个MIPS 特有的虚拟地址空间布局: 4G 的地址空间被分为四大区域。MIPS CPU 可以运行在两种特权级之上:用户态和核心态。当运行于用户态时只能访问到低2G 的kuseg 区域;而运行于核心态时,对于任意4个区域都能够正常访问。Vxworks 系统不分用户态和核心态,一律都运行在核心态。因此,我们的系统对整个虚拟地址空间都是可以正常访问的。 对于kuseg 区,其范围为0x00000000 – 0x7fffffff (低端2G),对这段空间的使用只有在ERL 置位,或是ERL 被清0,且TLB 已经正确配置的情况下才能进行。由于Cavium CPU特有的属性——对所有的内存空间的访问都是Cached,所以这段空间是一定Cached 的。 对于kseg0 区,其范围为0x80000000 – 0x9fffffff(共512M)。这段空间的访问不需要TLB 映射,只需将其最高位清0,即得到其相应的物理地址。该区域一定是Cached 的。 对于kseg1 区,其范围为0xa0000000 – 0xbfffffff (共512M )。这段空间通过去掉最高的三位来获得物理地址。因此,实际上它的物理地址范围同kseg0 是一致的。这段空间在MIPS 的定义中是unCached 的。但是由于上面提到的Cavium CPU 访问物理内存的特殊性,映射到这部分的0-256M 物理内存,访问时也是cached 的。MIPS 上电跳转的虚拟地址0xbfc00000 就是属于这段区域,其物理地址就是0x1fc00000。 对于 kseg2 区,其范围为 0xc0000000 – 0xffffffff (共 1G)。这块区域需要通过 TLB 才能够正确访问。 2. Cavium CPU 物理地址空间分布 Cavium 系列CPU 比较特别的地方,是其物理内存的物理地址是不连续的,即其DR1 DRAM 部分是0x410000000 – 0x41fffffff。这样做可能是因为其物理地址的0x10000000 – 0x1fffffff 在满足MIPS 的启动规则前提下分配给了boot-but 模块。如上图,当CPU 遇到0x10000000 – 0x1fffffff 的访问请求时,会将其转换为0x1000010000000 – 0x100001fffffff。这是因为在Cavium CPU 的物理地址空间中,分为两部分,即: System memory (DRAM) I/O space Caviu...