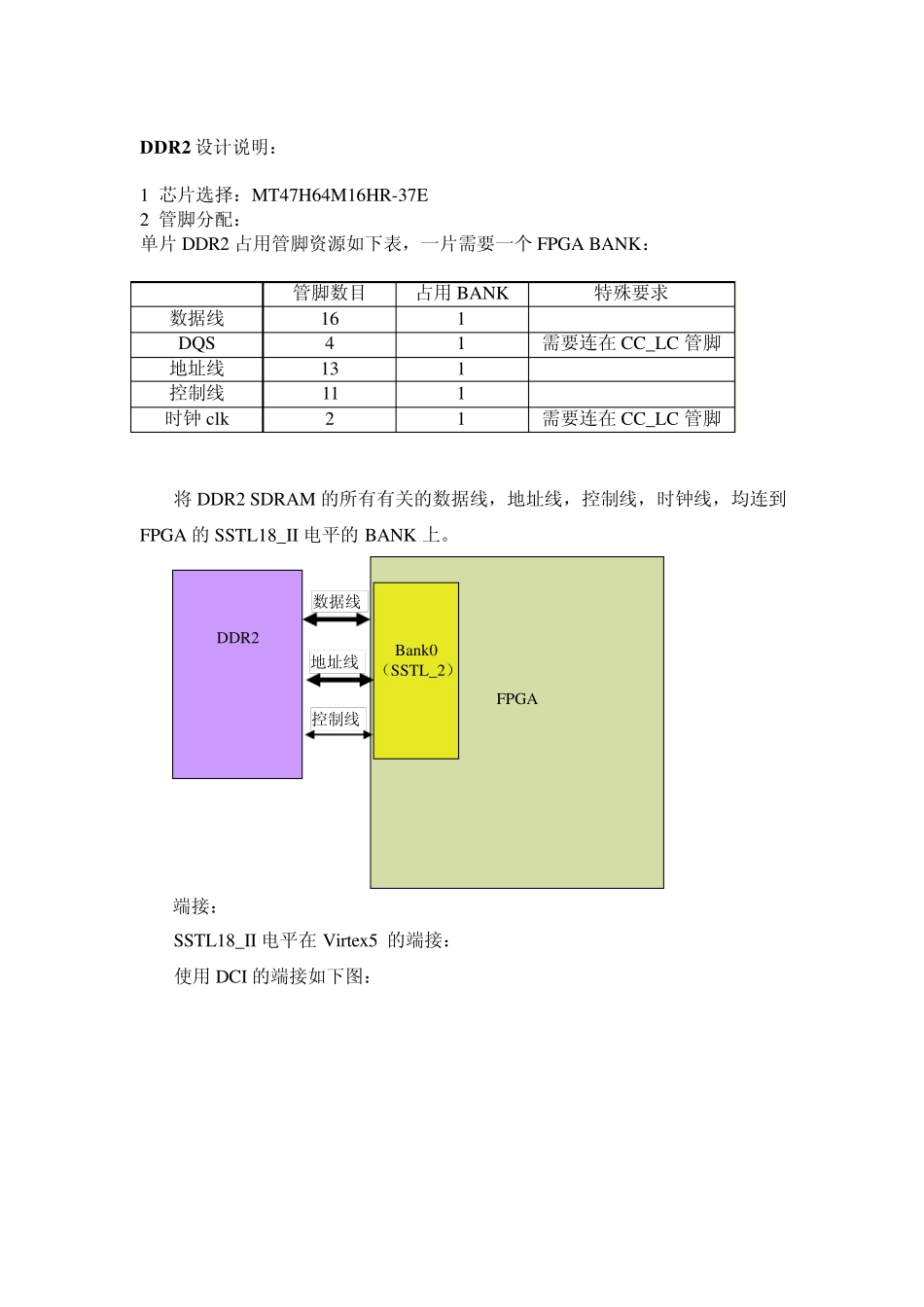

D D R 2 设计说明: 1 芯片选择:MT47H64M16HR-37E 2 管脚分配: 单片DDR2 占用管脚资源如下表,一片需要一个FPGA BANK: 管脚数目 占用BANK 特殊要求 数据线 16 1 DQS 4 1 需要连在CC_LC 管脚 地址线 13 1 控制线 11 1 时钟clk 2 1 需要连在CC_LC 管脚 将DDR2 SDRAM 的所有有关的数据线,地址线,控制线,时钟线,均连到FPGA 的SSTL18_II 电平的BANK 上。 DDR2 FPGA Bank0 (SSTL_2) 数据线 地址线 控制线 端接: SSTL18_II 电平在Virtex 5 的端接: 使用DCI 的端接如下图: 具体电路的连接参照我们已经调通的一个板卡原理图设计。主要是:DDR2数据线、DQS 信号等,与 FPGA 之间串接22 欧姆电阻;对时钟、地址信号和控制信号通过 47 欧姆的电阻上拉至 VTT(0.9V),PCB 设计上需要较多因素。 PCB 布线顺序:数据线-> 地址线-> 控制线 -> 时钟。其中数据线包括DQ/DQS/DM,它们都是在时钟的双沿发生操作。 PCB 布线要点: (1) 各种线的总长有要求; (2) 时钟(差分对)除了等长(< 50mil),要需要25mil 的安全距离。两个时钟 CK 之间相差 100mil 之内。 (3) 地址线不用等长,比时钟要长一些 (4) 控制线比时钟要长一些 (5) 每一个Data Grou p(8bits data + DQS + DM)在同一层走线。DDR2 的数据线与 DQS 是源同步关系,等长处理。同组的数据线以 DQS 基准等长(<50mil)。组与组之间的长度差不超过 1000mil。DQS 与 CK 之间的约束较弱,一般不考虑,长度差别不要超过 1000mil 就差不多。 (6) 地址/命令/控制信号与时钟是源同步的,走线长度匹配并不严格要求。 DDR2 SDRAM 的供电参见电源章节。 还需要注意的是,需要把DQS 信号都连接到IO_LxN_CC_LC 的管脚上。本时钟信号CK 是FPGA 输出给DDR2。 2 供电 (1)VDD = 1.8 V DDR2 SDRAM 内存的电流消耗取决于其容量的大小以及运行的环境和速度。 根据Micron 公司的数据手册(1GbDDR2.pdf),MT47H64M16HR-37E 在Operating bank interleav e read cu rrent 下IDD 的最大电流为350mA(颗粒是-187E,最大为520mA)。1.8V 同时还给FPGA 和PROM 供电,决定采用LT1764 来供电,最大输出电流是3A。 (2)VREF = 0.9V 基本上没有电流从DDR2 的VREF 管脚上流过,仅有微安级大小的漏电流。 (3)VTT = 0.9V 地址、命令和控制信号需要端接,IO ...