实验一 DFT Compiler 1

实验目的: 熟悉DFT Compiler 操作流程,完成对设计tcrm

v 的自动扫描链插入

回顾使用 Design Compile 进行逻辑综合的流程

实验内容: DFT Compiler 是一款功能强大的用于可测性设计的工具,提供从前端逻辑域到后端物理域完整的可测性设计解决方案,自动综合为带有扫描链的可测性设计

本文通过DFT Compiler 将设计tcrm

v 综合为带有扫描链的门级网表tcrm_scan

vg,并输出测试协议文件 tcrm_stil

spf,为进一步完成自动测试向量生成作数据准备

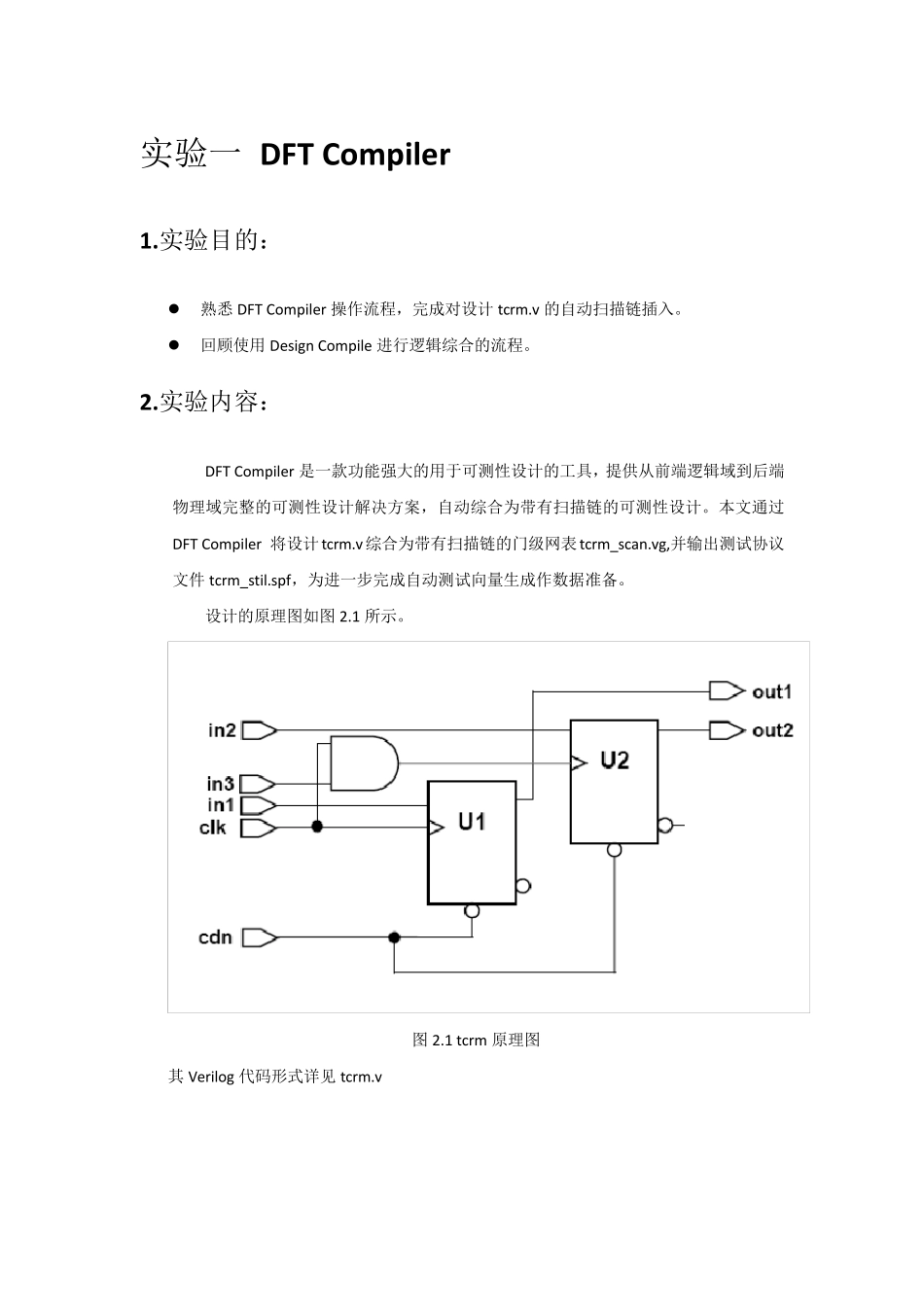

设计的原理图如图 2

1 tcrm 原理图 其 Verilog 代码形式详见 tcrm

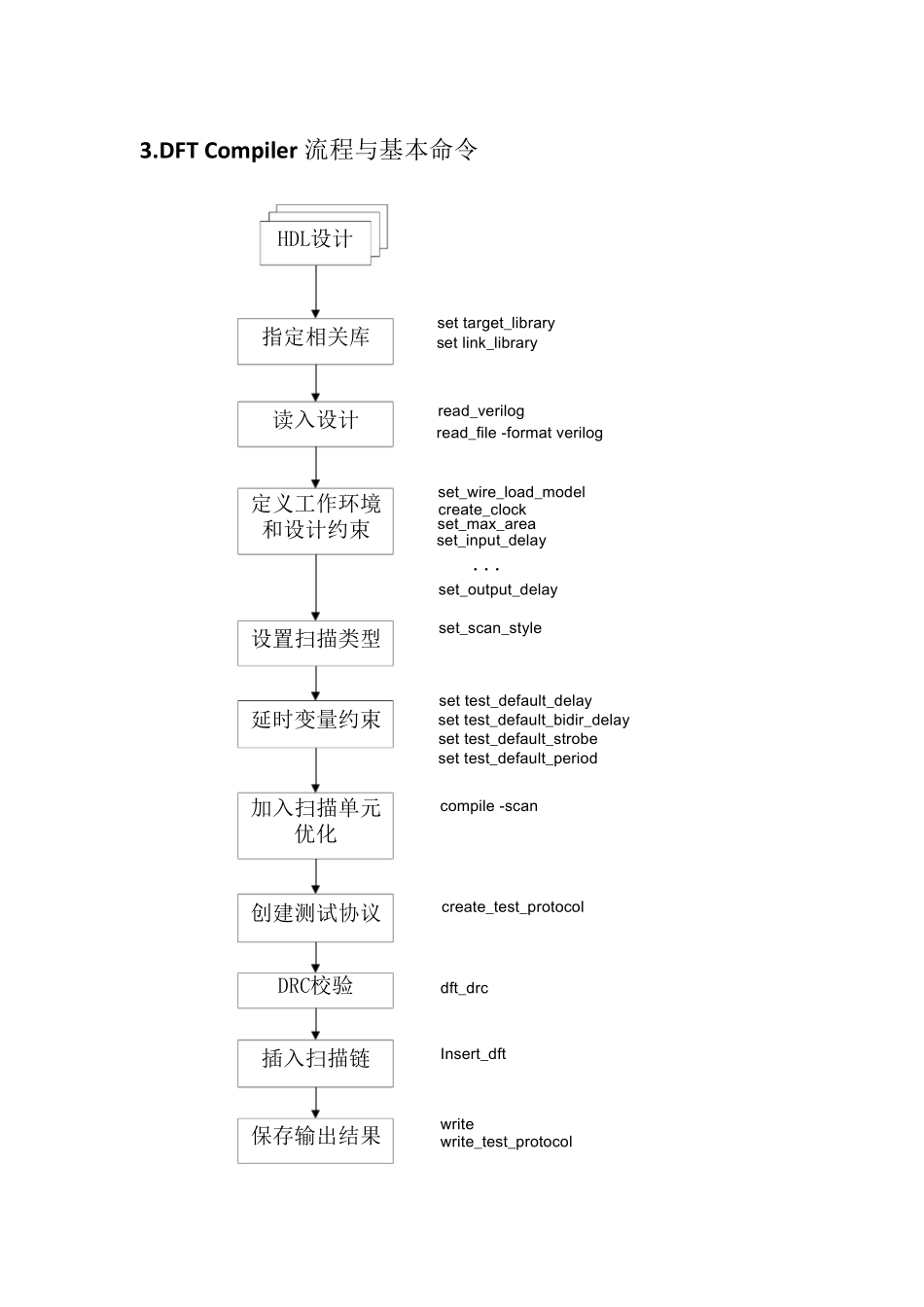

DFT Compiler流程与基本命令 指定相关库读入设计定义工作环境和设计约束设置扫描类型延时变量约束加入扫描单元优化创建测试协议DRC校验插入扫描链保存输出结果set target_library set link_libraryread_verilogread_file -format verilogset_wire_load_modelcreate_clockset_max_areaset_input_delay

set_output_delayset_scan_styleset test_default_delayset test_default_bidir_delayset test_default_strobeset test_default_periodcompile -scancreate_test_protocoldft_drcInsert_dftwritewrite_test_protocolHDL设计 4

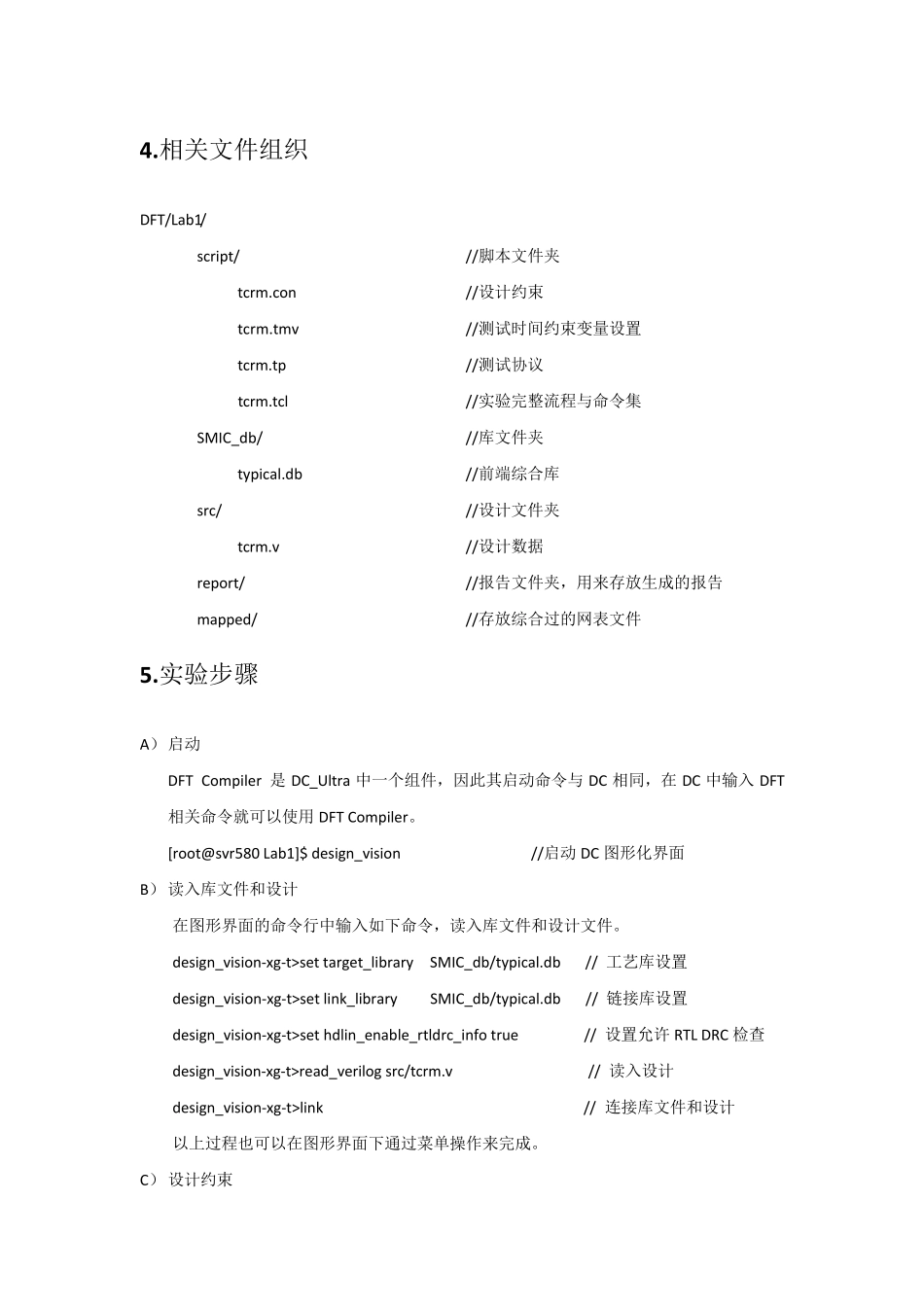

相关文件组织 DFT/Lab1/ script/ //脚本文件夹 t