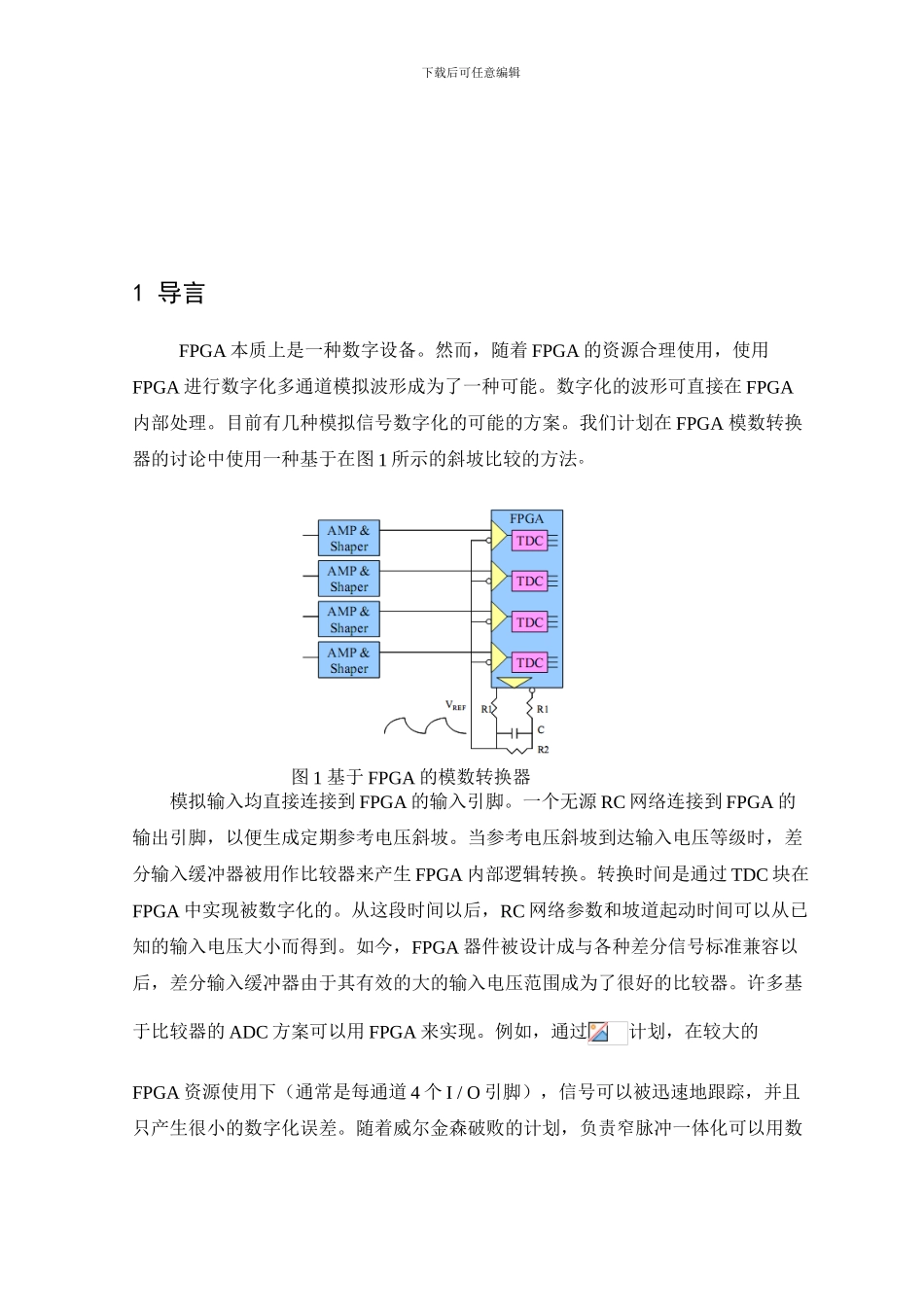

下载后可任意编辑毕业设计/论文外 文 文 献 翻 译 基于 FPGA 的数字信号发生器的设计 在现代电子测量技术的讨论及应用领域中,常常需要高精度且参数可调的信号源。数字信号发生器已成为现代测量领域应用最为广泛的通用仪器之一,代表了信号源的进展方向。而随着大规模可编程逻辑器件 FPGA 的进展以及可编程片上系统(SOPC)设计技术的日渐成熟,为这类信号发生器的设计与实现提供了理论依据与技术支持。本文设计的数字信号发生器以直接数字频率合成(DDS)技术为核心,用现场可编程门阵列(FPGA)来实现频率和相位的预置和改变,并完成信号的频率和相位差显示。设计中采纳的是直接数字频率合成(DDS)技术,该技术是一项关键的数字技术,能很好的实现信号在幅度,频率以及相位等方面的移动 。系统以 EDA 软件为工具,采纳 VHDL 语言,满足了对数字信号控制的更高要求。结果表明,采纳 EDA 技术设计的数字信号发生器使得数控系统与其他的电路实现的数字信号发生器相比具有更高的可靠性、实时性、运算速度高以及集成度高等特点。该数字信号发生器的设计可像软件一样随时更改,这就为系统维护带来了方便,同时结合 FPGA 有效地扩展输出波形的频率范围,实现了输出两路高精度相位差的正弦信号,使系统性能稳定可靠。 关键词:信号发生器;DDS;片上可编程系统;FPGA;下载后可任意编辑1 导言FPGA 本质上是一种数字设备。然而,随着 FPGA 的资源合理使用,使用FPGA 进行数字化多通道模拟波形成为了一种可能。数字化的波形可直接在 FPGA内部处理。目前有几种模拟信号数字化的可能的方案。我们计划在 FPGA 模数转换器的讨论中使用一种基于在图 1 所示的斜坡比较的方法。图 1 基于 FPGA 的模数转换器模拟输入均直接连接到 FPGA 的输入引脚。一个无源 RC 网络连接到 FPGA 的输出引脚,以便生成定期参考电压斜坡。当参考电压斜坡到达输入电压等级时,差分输入缓冲器被用作比较器来产生 FPGA 内部逻辑转换。转换时间是通过 TDC 块在FPGA 中实现被数字化的。从这段时间以后,RC 网络参数和坡道起动时间可以从已知的输入电压大小而得到。如今,FPGA 器件被设计成与各种差分信号标准兼容以后,差分输入缓冲器由于其有效的大的输入电压范围成为了很好的比较器。许多基于比较器的 ADC 方案可以用 FPGA 来实现。例如,通过计划,在较大的FPGA 资源使用下(通常是每通道 4 个 I / O 引脚),信号可以被迅...