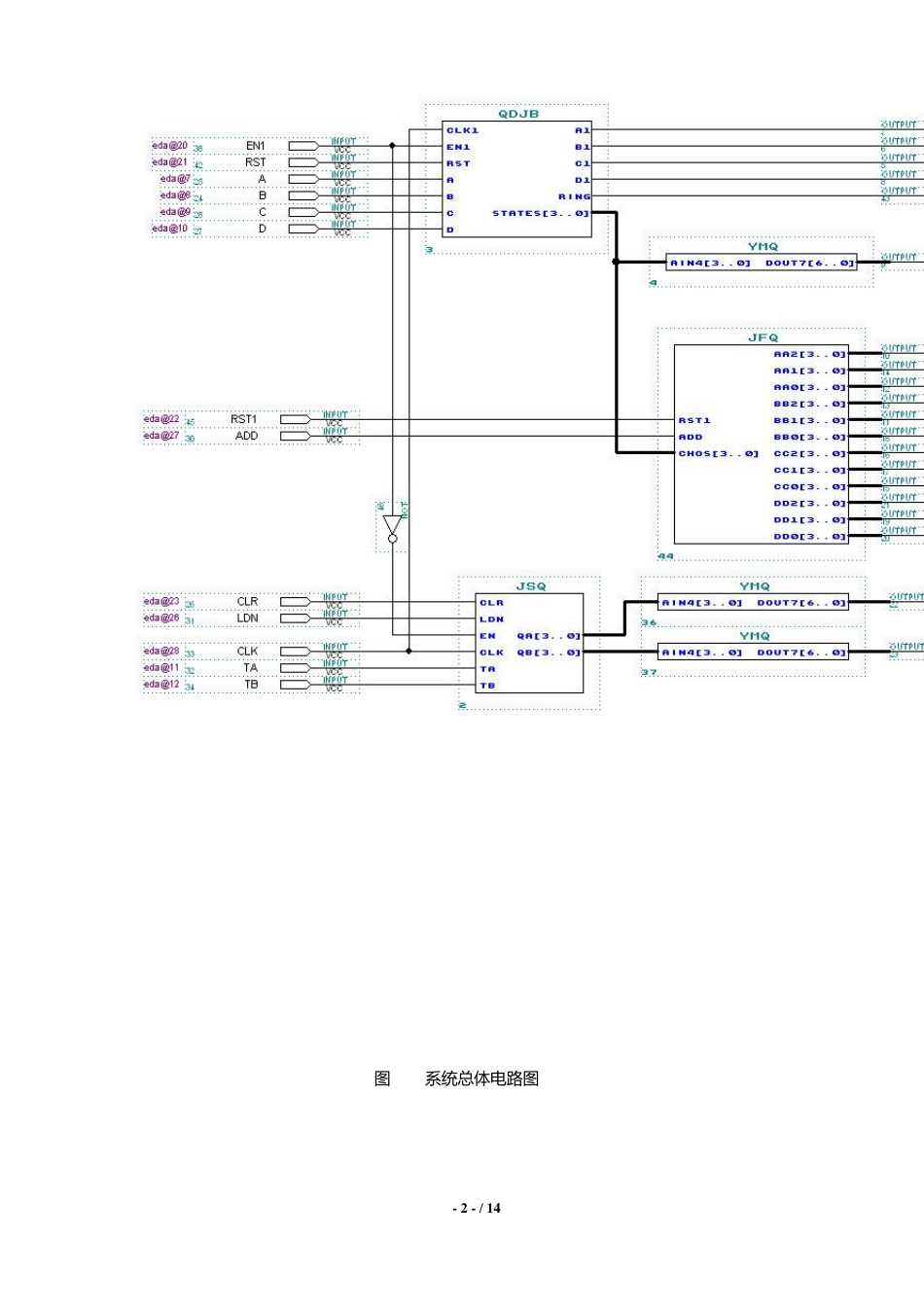

EDA 实习报告 设计课题: 数字式四路竞赛抢答器 - 1 - / 1 4 一、设计要求: 在许多比赛活动中,为了准确、公正、直观地判断出第一抢答者,通常设置一台抢答器,通过数显、灯光及音响等各种手段批示出第一抢答者。同时,还可以设置计分、犯规及奖惩记录等各种功能。本设计的具体功能是: 1.可容纳四组参赛者进行抢答,每组设置一个抢答按钮供抢答者使用。 2.电路具有第一抢答信号的鉴别和锁存功能。在主持人交系统复位并发出抢答指令后,若有一组先按下抢答开关,则该组指示灯亮并用组别显示电路显示抢答者的组别,同时扬声器发出“嘀嘟”的双音音响,且持续 2~3秒。此时,电路具备自锁功能,使他组的抢答开关不起作用。 3.具有计分功能,使每组在开始时的分数预置成100分,抢答后由主持人计分,答对一次加10分。 二、系统方案论证与模块划分: 根据系统设计要求可知: 1.系统的输入信号有:各组的抢答按钮 A、B、C、D,系统清零信号 CLR,系统时钟信号 CLK,计分复位端RST,加分按钮端ADD,计时预置控制端LDN,计时使能端EN,计时预置数据调整按钮 TA、TB; 2.系统的输出信号有:四个组抢答成功与否的指示灯控制信号输出口LED_A、LES_B、LED_C、LED_D,四个组抢答时的计时数码显示控制信号若干,抢答成功组别显示的控制信号若干,各组计分动态显示的控制信号若干。 3.本系统应具有的功能有:第一抢答信号的鉴别和锁存功能;抢答计时功能;各组得分的累加和动态显示功能。 根据以上的分析,我们可将整个系统分为三个主要模块:抢鉴别模块QDJB;抢答计时模块JSQ;抢答计分模块JFQ;对于需显示的信息,需增加或外接译码器,进行显示译码。考虑到FPGA、CPLD的可用接口及一般EDA实验开发系统的输出显示资源的限制,这里我们将组别显示和计时显示的译码器内设,而将各组的计分显示的译码器外接。整个系统的组成框图如图2-1所示: 系统的工作原理如下:当主持人按下使能端EN1时,抢答器开始工作,A、B、C、D四个抢答者谁最先抢答成功则此选手的台号灯(LED_A—LED_D)将点亮,并且组别显示数码管将显示出抢答成功者的台号,并由蜂鸣器发出抢答成功的警报;接下来主持人提问,若回答正确,主持人按加分按钮 ADD,抢答计分模块JFQ将给对应的组加分,并将该组的总分显示在对应的选手计分数码管 JF2_A-JF0_A、JF2_B-JF0_B、JF2_C-JF0_C、JF2_D-JF0_D、上。在此过程中,主持人可以采用计时手段(JSQ模块),打开计时器使计时预置控...