综合实验报告 第四组 组长: 韩欢 0 2 0 8 1 5 3 5 陈洁钰 0 2 0 8 1 5 3 6 侯旭涛 0 2 0 8 1 5 1 4 高耀 0 2 0 8 1 5 1 0 李欣昊 0 2 0 8 1 5 0 8 李昊 0 2 0 8 1 5 0 6 FPGA 基础试验之流水灯 一、实验目的 通过此实验进一步了解、熟悉和掌握 Qu artu s II开发软件的使用方法及 Verilog语言的编程方法

学习简单时序电路的设计分析和硬件测试

二、实验内容 1.熟悉信号产生板中的 FPGA 的普通 I/O 的连接; 2.根据实际的流水灯分析时序,体会用 Verilog 语言的编程产生相应时序; 3.熟悉集成开发工具 Qu artu s II,学会使用 Qu artu s II 对 Cy clone 系列 FPGA 的程序开发、编译与调试; 4.掌握 Cy clone 系列 FPGA 的程序加载,熟练掌握将

sof 文件加载到实验板的FPGA 中,实现流水灯的效果

三、实验原理 流水灯,顾名思义就是让 LED 像水一样的点亮

如果把流水做慢动作播放,可以想象到其实就是移动,即:把水块不断地向同一方向移动,而原来的水块保持不动,就形成了流水

同样,如果使得最左边的灯先亮,然后通过移位,在其右侧的灯,从左向右依次点亮,而已经亮的灯又不灭,便形成了向右的流水灯

初始状态时,四个灯都不亮,每来一个时钟脉冲,CLK,计数器就加 1

这样通过移位依次点亮所有的灯,就形成了流水灯

而当四个灯都点亮时,需要一个操作使得所有的灯恢复为初始状态

然后,再一次流水即可

如果是右移位,就出现向右流水的现象;反之,向左流水

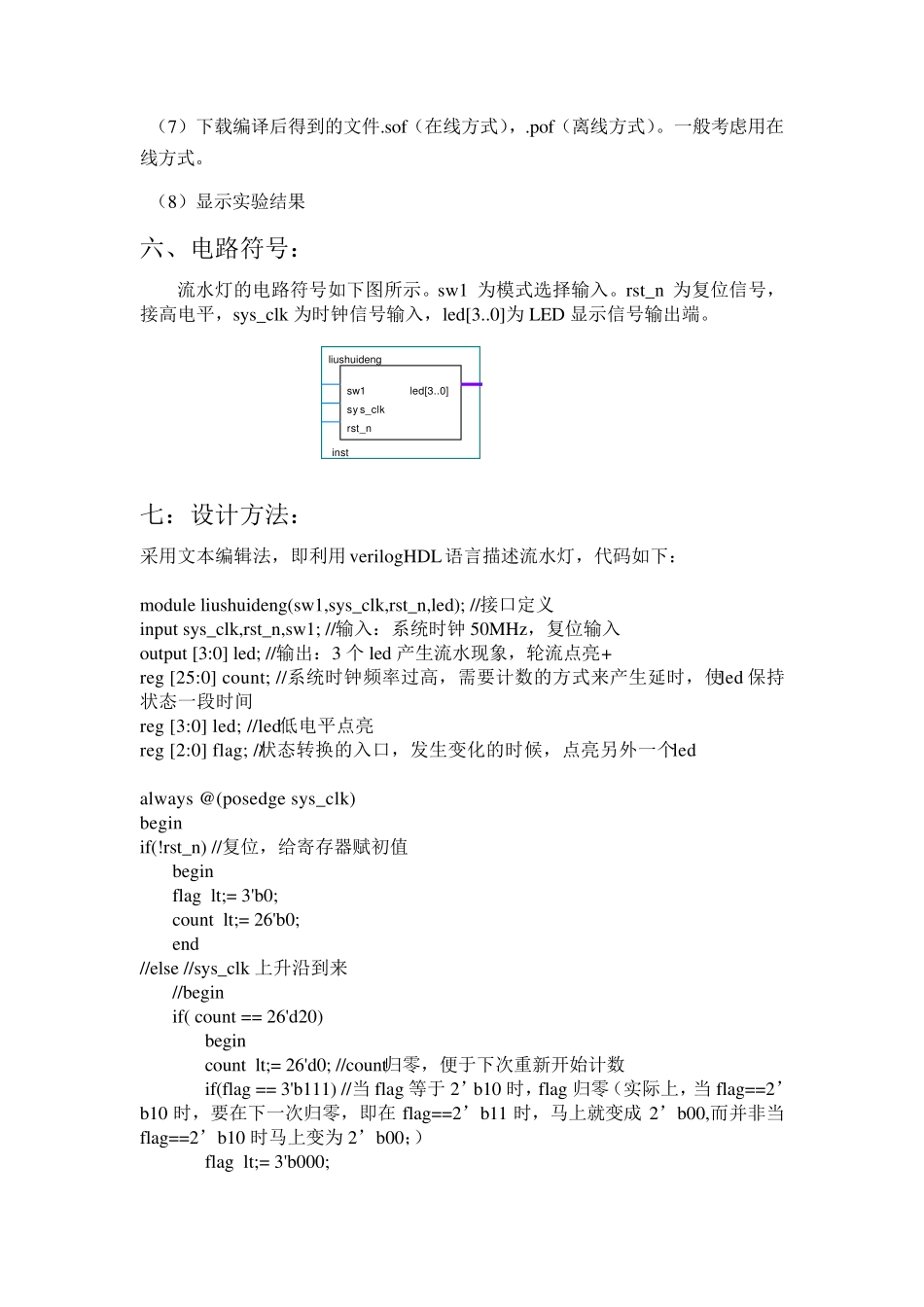

四、实验要求 控制 4 个 LED 进行花式显示,根据硬件设施设计两种模式: S0:从全亮到全灭,再到全亮,依次循环;S1:从 LED0 开始依次点亮,为 LED1 亮