本文为edacn

net 特约创作,作者dev e 第一编 验证的重要性 验证,顾名思义就是通过仿真、时序分析、上板调试等手段检验设计正确性的过程,在FPGA/IC开发流程中,验证主要包括功能验证和时序验证两个部分

为了了解验证的重要性,我们先来回顾一下 FPGA开发的整个流程

FPGA开发流程和 IC的开发流程相似,主要分为以下几个部分: 1)设计输入,利用 HDL输入工具、原理图输入工具或状态机输入工具等把所要设计的电路描述出来

2)功能验证,也就是前仿真,利用 Modelsim、VCS等仿真工具对设计进行仿真,检验设计的功能是否正确;常用的仿真工具有 Model Tech公司的 ModelSim,Synopsys公司的VCS,Cadence公司的 NC-Verilog和 NC-VHDL,Aldec公司的 Active HDL VHDL/Verilog HDL等

仿真过程能及时发现设计中的错误,加快了设计进度,提高了设计的可靠性

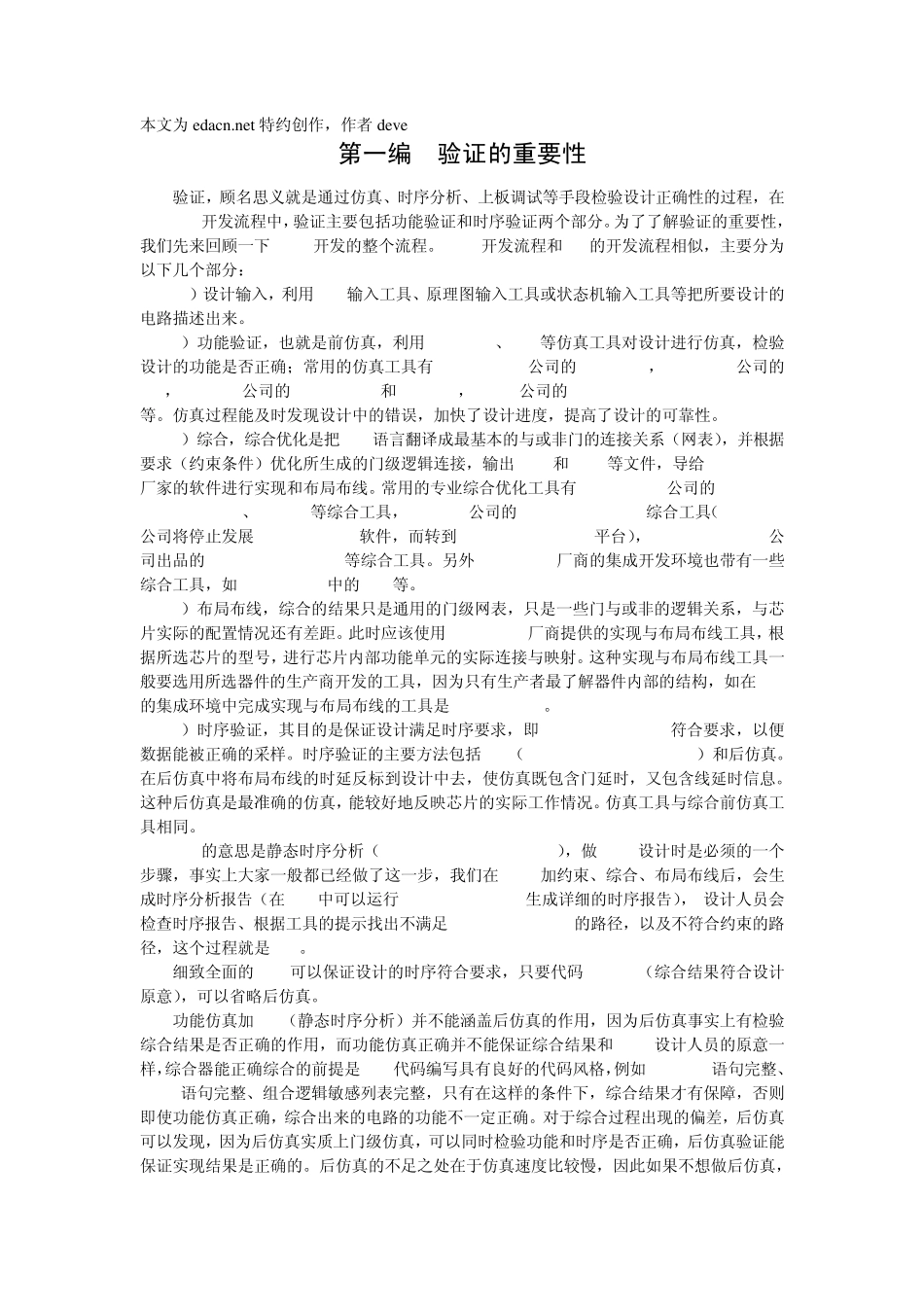

3)综合,综合优化是把 HDL语言翻译成最基本的与或非门的连接关系(网表),并根据要求(约束条件)优化所生成的门级逻辑连接,输出 edf和 edn等文件,导给 CPLD/FPGA厂家的软件进行实现和布局布线

常用的专业综合优化工具有 Synplicity公司的 synplify /Synplify Pro、Amplify等综合工具,Synopsys公司的 FPGA Compiler II综合工具(Synopsys公司将停止发展 FPGA Express软件,而转到 FPGA Compiler II平台),Exemplar Logic公司出品的 LeonardoSpectrum等综合工具

另外 FPGA/CPLD厂商的集成开发环境也带有一些综合工具,如 Xilinx ISE中的 XST等

4)布局布线,综合的结果只是通用的门级网表,只是一些