随着移动消费型电子产品对于小型化,功能集成以及大存储空间的要求的进一步提升,元器件的小型化高密度封装形式也越来越多,如多模块封装(MCM),系统封装(SiP),倒装晶片等应用得越来越多

而元件堆叠装配(PoP, Pa ckage on Package)技术的出现更加模糊了一级封装与二级装配之间的界线,在大大提高逻辑运算功能和存储空间的同时,也为终端用户提供了自由选择器件组合的可能,生产成本也得以更有效的控制

对于3G 手机 PoP 无疑是一个值得考虑的优选方案

勿庸置否,随着小型化高密度封装的出现,对高速与高精度装配的要求变得更加关键

相关的组装设备和工艺也更具先进性与高灵活性

元器件堆(Package on Package)技术必须经受这一新的挑战

元器件堆叠装配技术市场情况及其推动力 当前半导体封装发展的趋势是越来越多的向高频、多芯片模块(MCM),系统集成(SiP)封装,堆叠封装(PiP, PoP)发展,从而传统的装配等级越来越模糊,出现了半导体装配与传统电路板装配间的集成,如倒装晶片(Flip Chip)直接在终端产品装配

半导体装配设备中的特征功能开始出现在多功能精细间距贴片机上,同时具有较高的精度,又有助焊剂应用的功能

可以说,元件堆叠技术是在业已成熟的倒装晶片装配技术上发展起来的

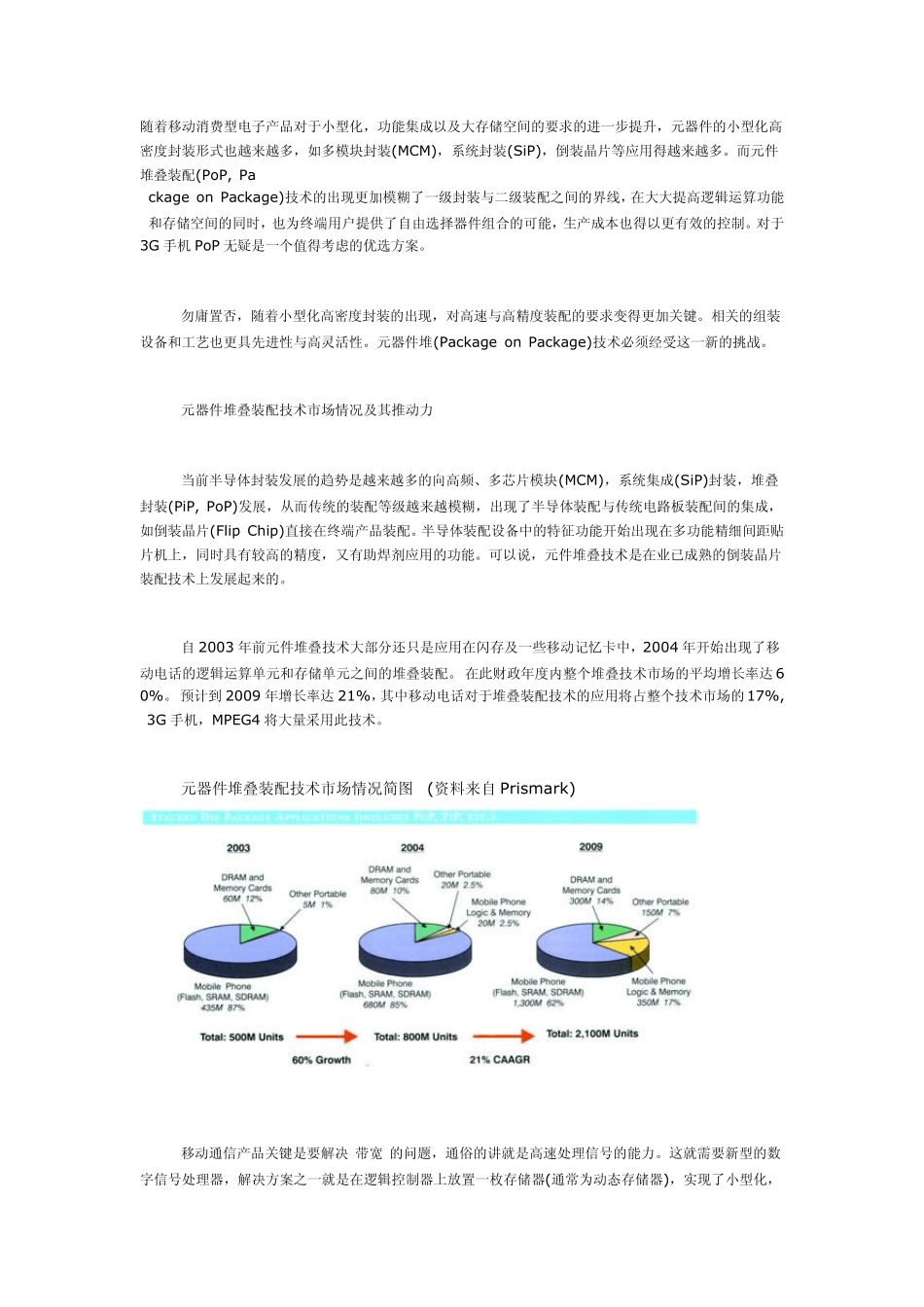

自 2003 年前元件堆叠技术大部分还只是应用在闪存及一些移动记忆卡中,2004 年开始出现了移动电话的逻辑运算单元和存储单元之间的堆叠装配

在此财政年度内整个堆叠技术市场的平均增长率达 60%

预计到 2009 年增长率达 21%,其中移动电话对于堆叠装配技术的应用将占整个技术市场的17%, 3G 手机,MPEG4 将大量采用此技术

元器件堆叠装配技术市场情况简图 (资料来自 Prismark) 移动通信产品关键是要解决”带宽”的问题,通俗的讲就是高速处理信号的能力