某计算机的主存地址空间中,从地址 0000H 到 3FFFH 为 ROM 存储区域,从 4000H 到 5FFFH为保留地址区域,临时不用,从 6000H 到 FFFFH 为 RAM 地址区域

RAM 的控制信号为 CS#和WE#,CPU 的地址线为 A15~A0,数据线为 8 位的线路 D7~D0,控制信号有读写控制 R/W#和访存请求 MREQ#,要求: (1) 假如 ROM 和 RAM 存储器芯片都采纳 8K×1 的芯片,试画出存储器与 CPU 的连接图

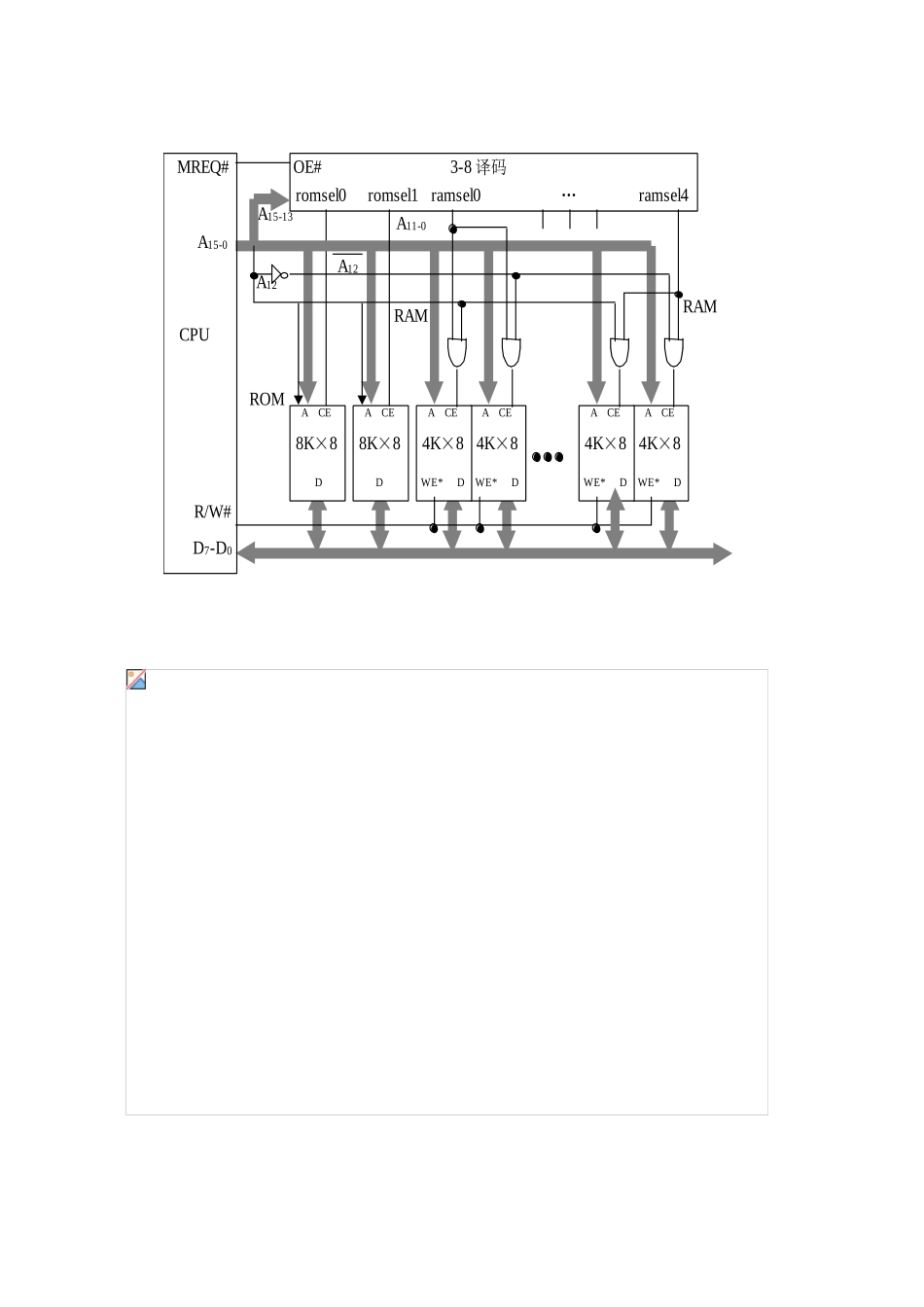

(2) 假如 ROM 存储器芯片采纳 8K×8 的芯片,RAM 存储器芯片采纳 4K×8 的芯片,试画出存储器与 CPU 的连接图

(3) 假如 ROM 存储器芯片采纳 16K×8 的芯片,RAM 存储器芯片采纳 8K×8 的芯片,试画出存储器与 CPU 的连接图

ramsel43-8 译码ramsel0romsel1romsel0…A15-13A15-0A12A12A11-0RAMRAMROMOE#MREQ#R/W#CPUD7-D0A CE4K×8WE* DA CE4K×8WE* DA CE4K×8WE* DA CE4K×8WE* DA CE8K×8DA CE8K×8 D一. 假设主存只有 a,b,c 三个页框,组成 a 进 c 出的 FIFO 队列,进程访问页面的序列是 0,2,5,4,5,2,5,2,3,5,2,4 号

用列表法求采纳 FIFO+LRU 替换策略时的命中率

(10 分)【解】求解表格如下所示二. 指令流水线有取指(IF)、译码(ID)、执行(EX)、访存(MEM)、写回寄存器堆(WB) 5 个过程段,共有 15 条指令连续输入此流水线

(1)画出流水处理的时空图,假设时钟周期为 100ns

(2)求流水线的实际吞吐率(单位时间里执行完毕的指令数)

(10 分)【解】(1)SI1I2I3I4