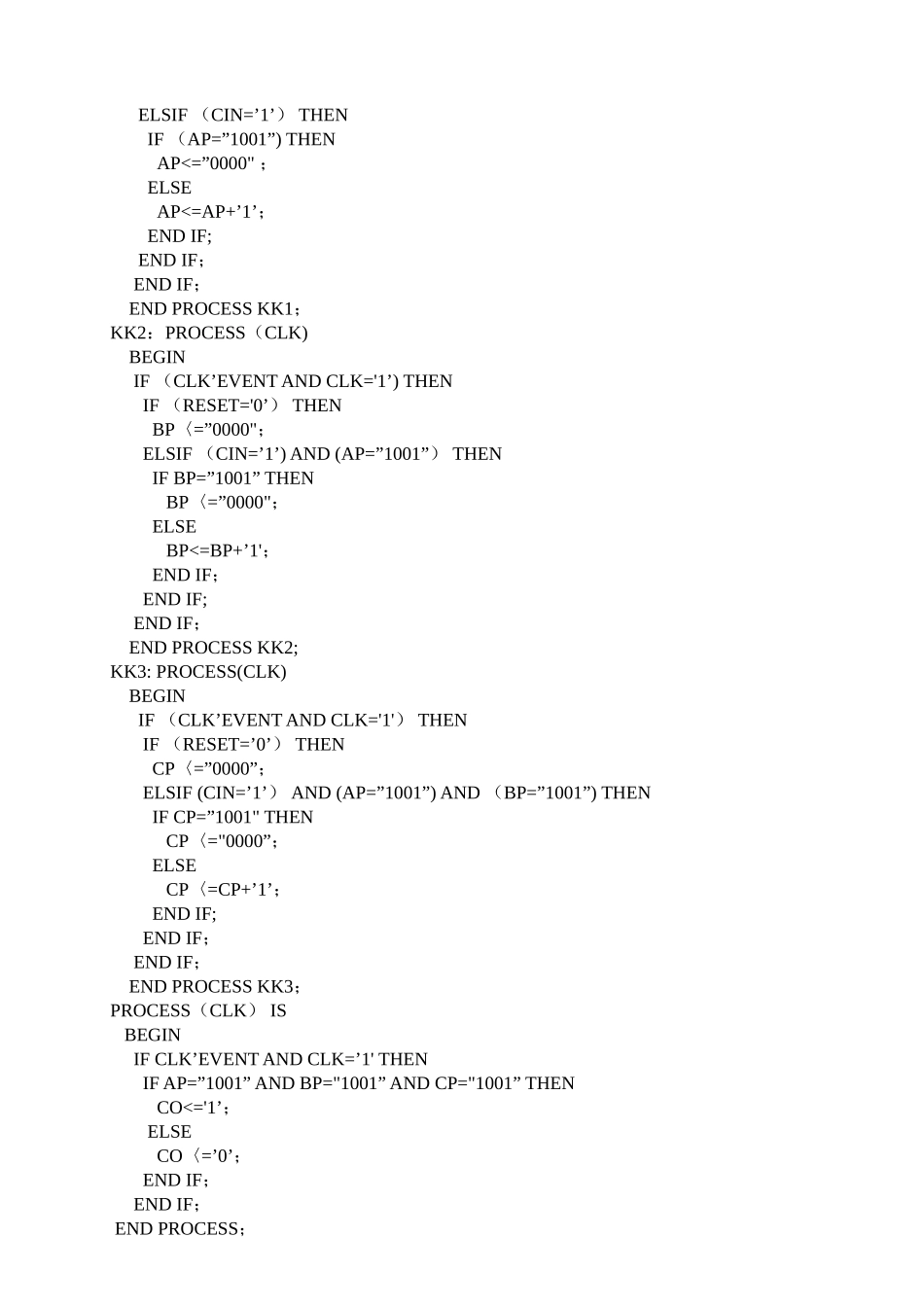

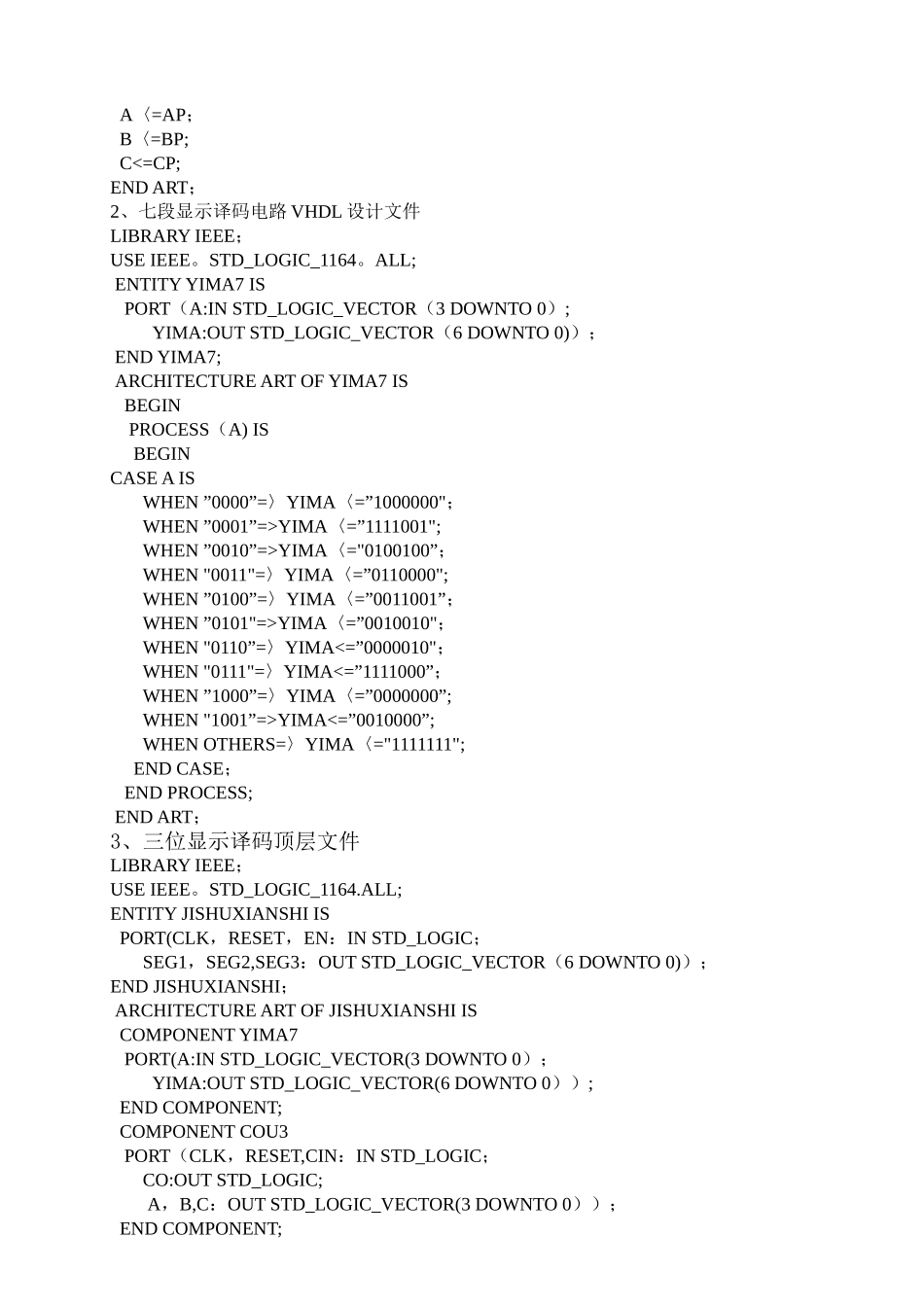

本科课程设计报告课程名称: EDA 计数与 FPGA 应用设计 设计题目:交通灯控制器 实验地点: 跨越机房专业班级:电信 090 1 学号:20240012 49 学生姓名:赵岩 指导老师:张文爱年 月 日设计一:三位十进制计数显示器一、 设计目的:1、掌握时序电路中多进程的 VHDL 的描述方法.2、掌握层次化设计方法。3、熟悉 EDA 的仿真分析和硬件测试技术。二、设计原理三位十进制计数显示器分三部分完成,先设计十进制计数电路,再设计显示译码电路,最后设计一个顶层文件将两者连接起来。三源程序1、三位十进制计数器的三位分三个进程描述,含有同步清 0 信号 RESET和计数使能控制信号 CINLIBRARY IEEE;USE IEEE.STD_LOGIC_1164。ALL;USE IEEE。STD_LOGIC_UNSIGNED.ALL;ENTITY COU3 IS PORT(CLK,RESET,CIN:IN STD_LOGIC; CO:OUT STD_LOGIC; A,B,C:OUT STD_LOGIC_VECTOR(3 DOWNTO 0)); END COU3 ;ARCHITECTURE ART OF COU3 IS SIGNAL AP,BP,CP:STD_LOGIC_VECTOR(3 DOWNTO 0); BEGIN KK1:PROCESS(CLK) BEGIN IF (CLK'EVENT AND CLK=’1') THEN IF (RESET=’0') THEN AP〈=”0000"; ELSIF (CIN=’1’) THEN IF (AP=”1001”) THEN AP<=”0000" ; ELSE AP<=AP+’1’; END IF; END IF; END IF; END PROCESS KK1;KK2:PROCESS(CLK) BEGIN IF (CLK’EVENT AND CLK='1’) THEN IF (RESET='0’) THEN BP〈=”0000"; ELSIF (CIN=’1’) AND (AP=”1001”) THEN IF BP=”1001” THEN BP〈=”0000"; ELSE BP<=BP+’1'; END IF; END IF; END IF; END PROCESS KK2;KK3: PROCESS(CLK) BEGIN IF (CLK’EVENT AND CLK='1') THEN IF (RESET=’0’) THEN CP〈=”0000”; ELSIF (CIN=’1’) AND (AP=”1001”) AND (BP=”1001”) THEN IF CP=”1001" THEN CP〈="0000”; ELSE CP〈=CP+’1’; END IF; END IF; END IF; END PROCESS KK3;PROCESS(CLK) IS BEGIN IF CLK’EVENT AND CLK=’1' THEN IF AP=”1001” AND BP="1001” AND CP="1001” THEN CO<='1’; ELSE CO〈=’0’; END IF; END IF; END PROCESS; A〈=AP; B〈=BP; C<=CP;END ART;2、七段显示译码电路 VHDL 设计文件LIBRARY IEEE;USE IEEE。STD_LOGIC_1164。ALL; ENTIT...