实验十一、基于重叠和流水线技术的 CPU 结构实验一、实验目的: 1

了解微程序控制器是如何控制模型机运营的,掌握整机动态工作过程; 2

掌握重叠和流水线结构的工作原理及实现方法; 3

定义五条机器指令,编写相应微程序并具体上机调试

二、实验设备:EL-JY-II 型计算机组成原理实验系统一套,排线若干

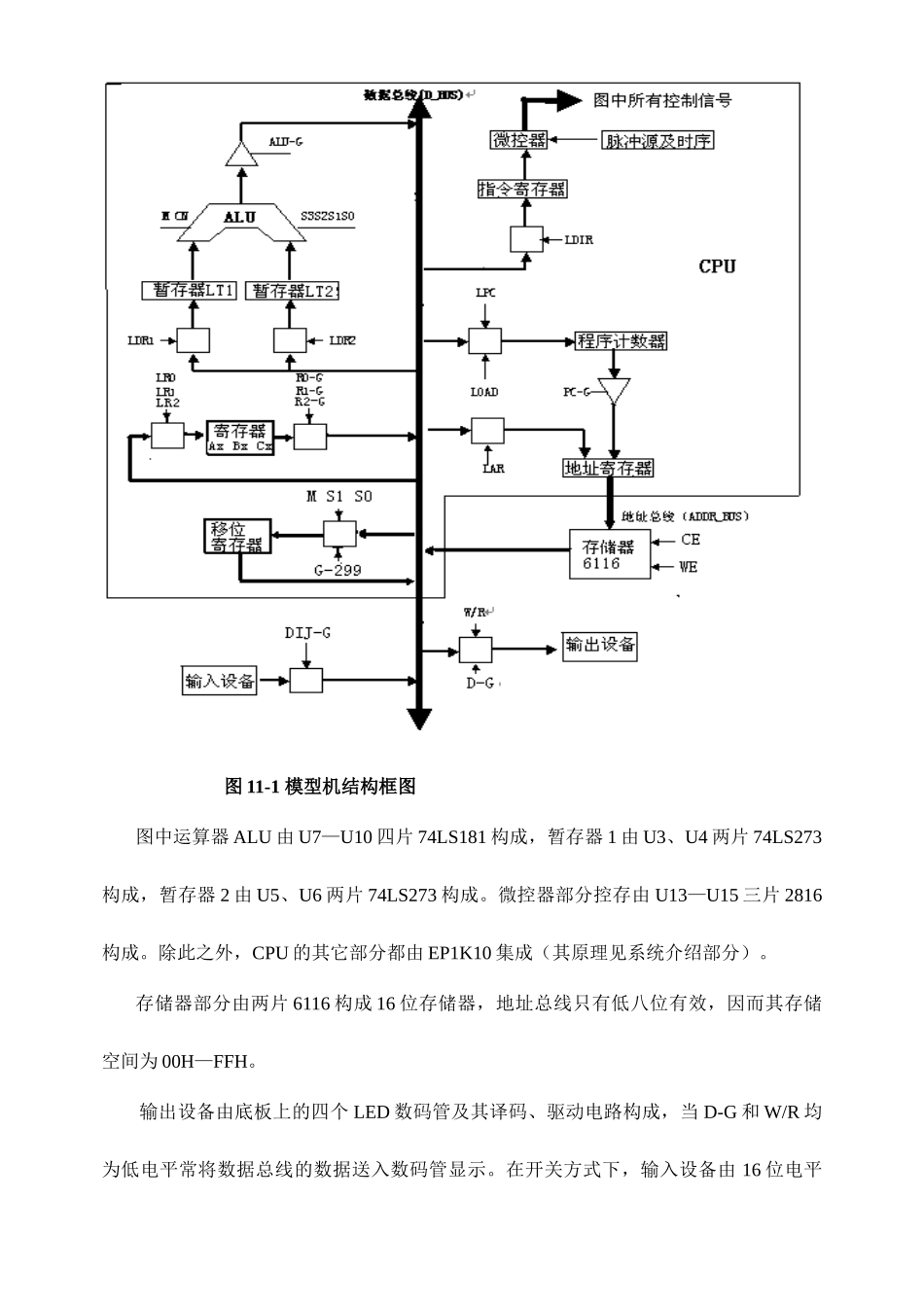

三、模型机结构: 图 11-1 模型机结构框图图中运算器 ALU 由 U7—U10 四片 74LS181 构成,暂存器 1 由 U3、U4 两片 74LS273构成,暂存器 2 由 U5、U6 两片 74LS273 构成

微控器部分控存由 U13—U15 三片 2816构成

除此之外,CPU 的其它部分都由 EP1K10 集成(其原理见系统介绍部分)

存储器部分由两片 6116 构成 16 位存储器,地址总线只有低八位有效,因而其存储空间为 00H—FFH

输出设备由底板上的四个 LED 数码管及其译码、驱动电路构成,当 D-G 和 W/R 均为低电平常将数据总线的数据送入数码管显示

在开关方式下,输入设备由 16 位电平开关及两个三态缓冲芯片 74LS244 构成,当 DIJ-G 为低电平常将 16 位开关状态送上数据总线

在键盘方式或联机方式下,数据可由键盘或上位机输入,然后由监控程序直接送上数据总线,因而外加的数据输入电路可以不用

注:本系统的数据总线为 16 位,指令、地址和程序计数器均为 8 位

当数据总线上的数据打入指令寄存器、地址寄存器和程序计数器时,只有低 8 位有效

四、工作原理重叠技术的原理为:程序开始执行时,先将若干条指令取入一个先进先出(FIFO)的指令队列

然后在指令译码的同时,从 FIFO 队列中取出下一条指令,打入指令寄存器,使得“取指令”和“执行指令”具有时空上的并行性

流水线技术是建立在重叠技术的基础上

本实验采纳二级流水线结构,其原