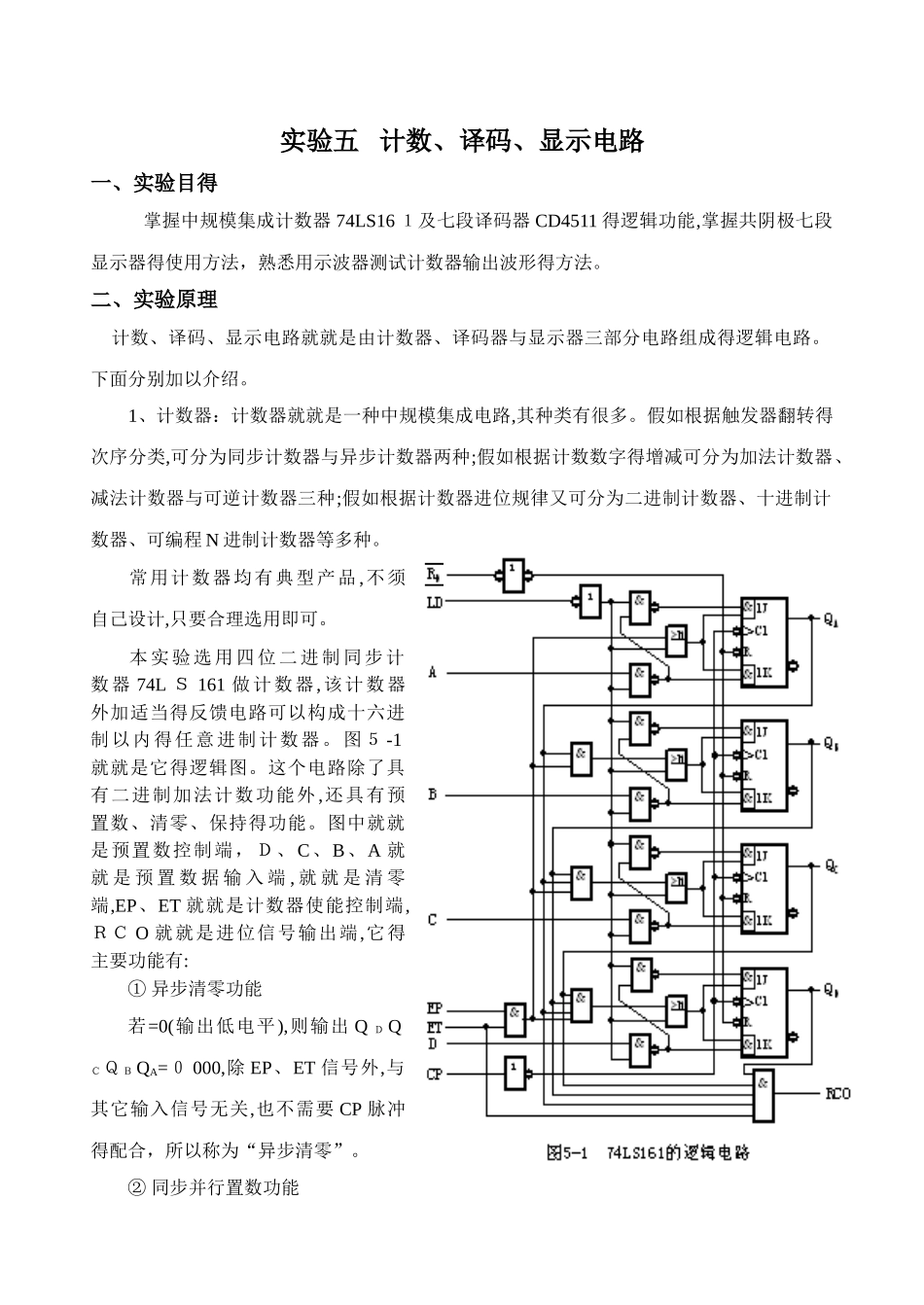

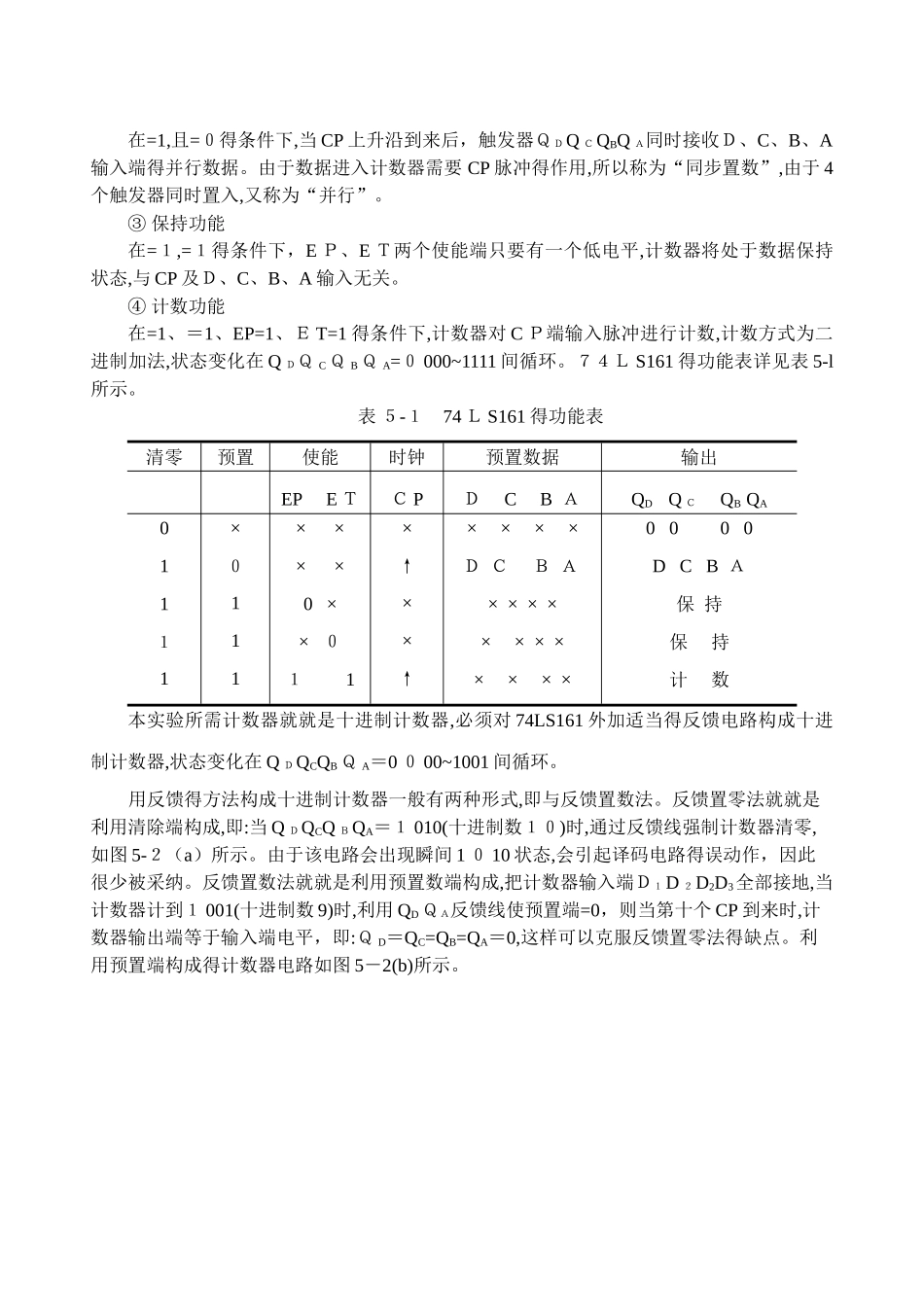

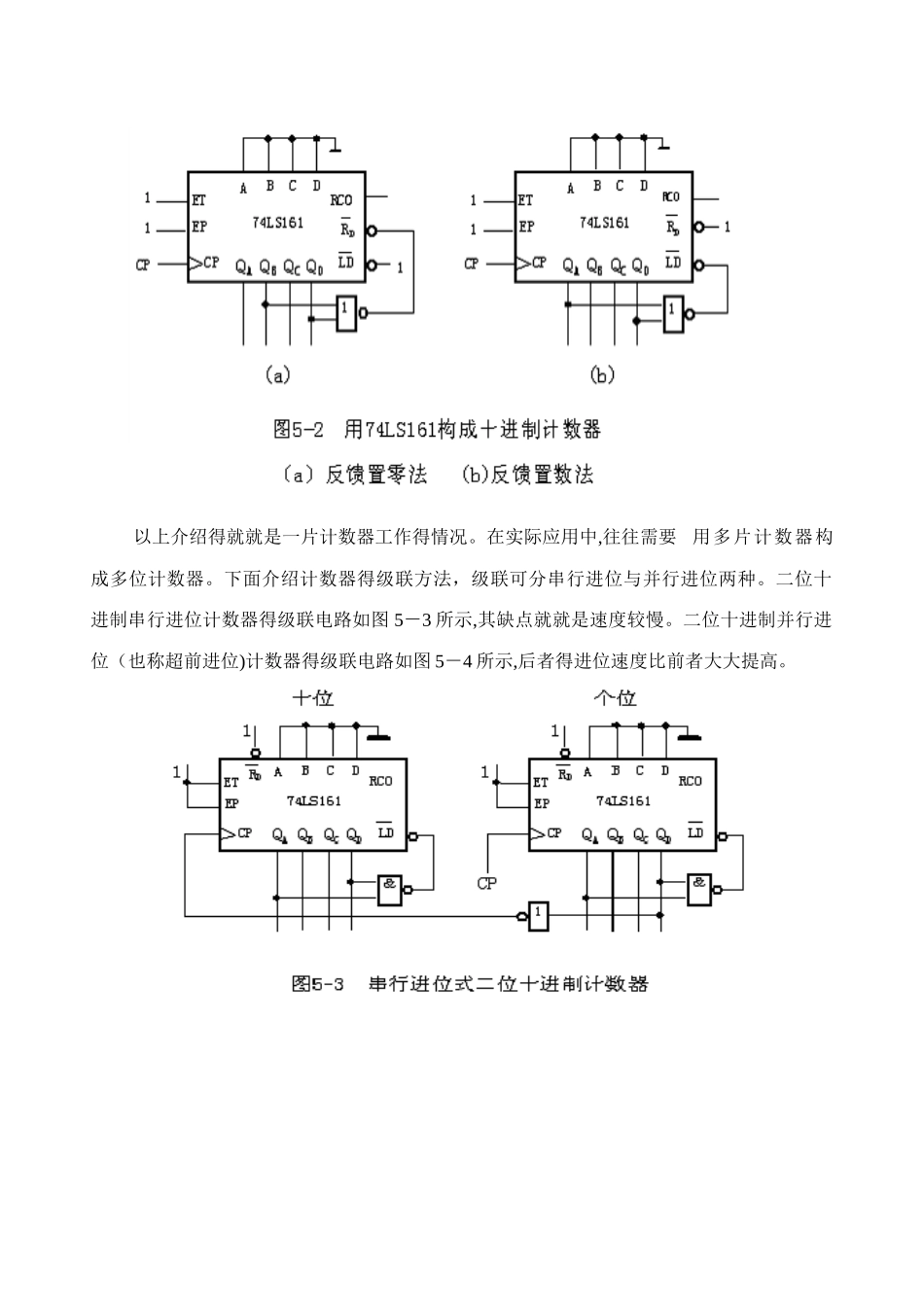

实验五 计数、译码、显示电路一、实验目得 掌握中规模集成计数器 74LS16 1及七段译码器 CD4511 得逻辑功能,掌握共阴极七段显示器得使用方法,熟悉用示波器测试计数器输出波形得方法。二、实验原理 计数、译码、显示电路就就是由计数器、译码器与显示器三部分电路组成得逻辑电路。下面分别加以介绍。1、计数器:计数器就就是一种中规模集成电路,其种类有很多。假如根据触发器翻转得次序分类,可分为同步计数器与异步计数器两种;假如根据计数数字得增减可分为加法计数器、减法计数器与可逆计数器三种;假如根据计数器进位规律又可分为二进制计数器、十进制计数器、可编程 N 进制计数器等多种。常用计数器均有典型产品 ,不须自己设计,只要合理选用即可。本 实 验 选 用 四 位 二 进 制 同 步 计数器 74L S 161 做计数器,该计数器外加适当得反馈电路可以构成十六进制以内得任意进制计数器。图5 -1就就是它得逻辑图。这个电路除了具有二进制加法计数功能外 ,还具有预置数、清零、保持得功能。图中就就是预置数控制端,D、 C、B、A 就就 是 预 置 数 据 输 入 端 , 就 就 是 清 零端,EP、ET 就就是计数器使能控制端,RC O 就就是进位信号输出端,它得主要功能有:① 异步清零功能 若=0(输出低电平),则输出 Q D QCQB QA=0 000,除 EP、ET 信号外,与其它输入信号无关,也不需要 CP 脉冲得配合,所以称为“异步清零”。② 同步并行置数功能在=1,且=0得条件下,当 CP 上升沿到来后,触发器QDQ CQBQ A同时接收D、C、B、A输入端得并行数据。由于数据进入计数器需要 CP 脉冲得作用,所以称为“同步置数”,由于 4个触发器同时置入,又称为“并行”。③ 保持功能在=1,=1得条件下,E P、E T两个使能端只要有一个低电平,计数器将处于数据保持状态,与 CP 及D、C、B、A 输入无关。④ 计数功能在=1、=1、EP=1、E T=1 得条件下,计数器对 C P端输入脉冲进行计数,计数方式为二进制加法,状态变化在 Q DQ CQ BQ A=0 000~1111 间循环。74L S161 得功能表详见表 5-l所示。表 5-1 74 L S161 得功能表清零预置使能时钟预置数据输出EP E TC PD C B AQD Q C QB QA01111×0111× ×× ×0 ×× 01 1×↑××↑× × × ×D C B A× × × ×× × × ×× × × ×0 0 0 0D C B A保 持保 持计 数本...