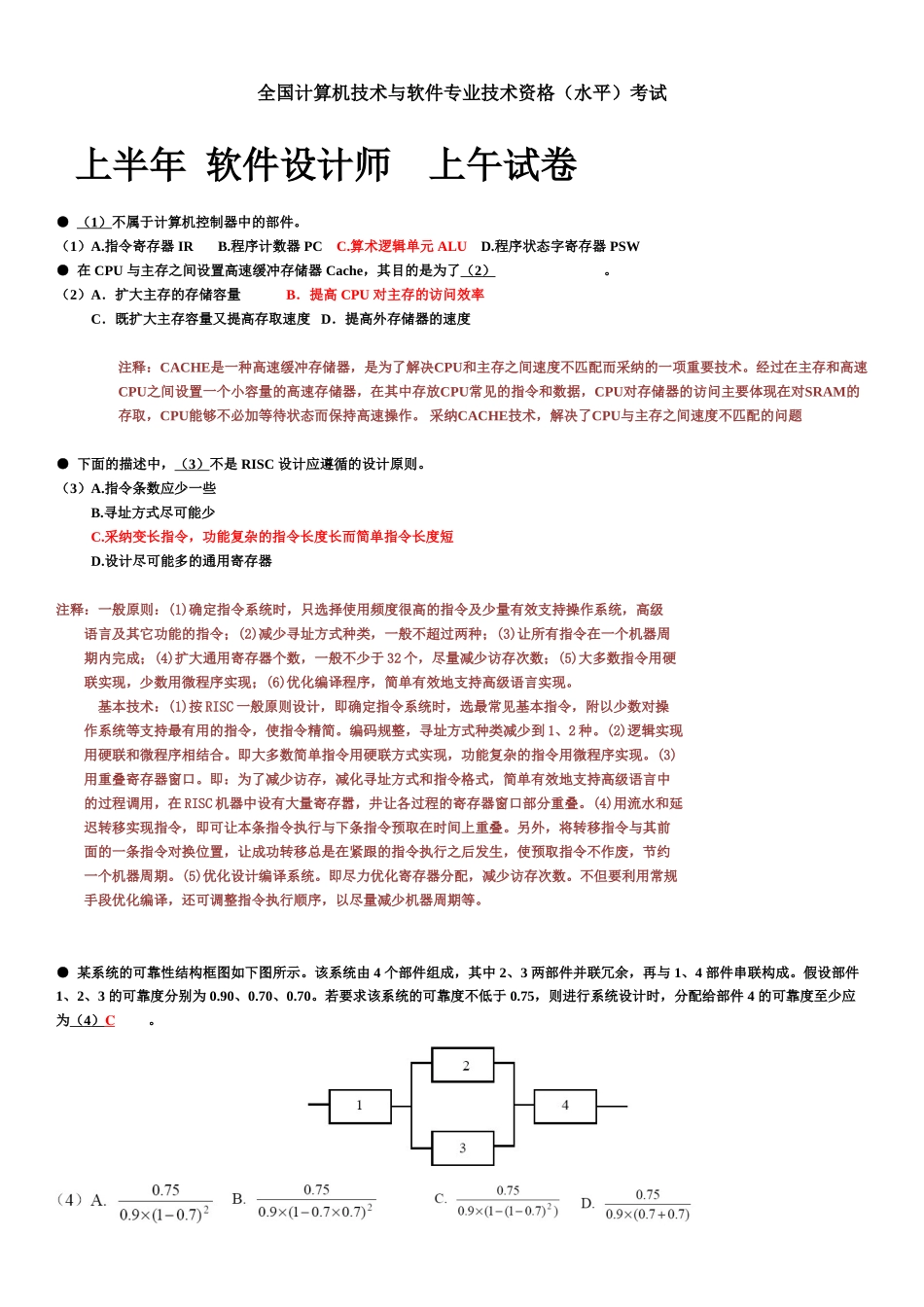

软件设计师考试历年真题及答案全国计算机技术与软件专业技术资格(水平)考试 上半年 软件设计师 上午试卷● ( 1 ) 不属于计算机控制器中的部件

指令寄存器 IR B

程序计数器 PC C

算术逻辑单元 ALU D

程序状态字寄存器 PSW● 在 CPU 与主存之间设置高速缓冲存储器 Cache,其目的是为了( 2 )

(2)A.扩大主存的存储容量 B.提高 CPU 对主存的访问效率C.既扩大主存容量又提高存取速度 D.提高外存储器的速度注释:CACHE是一种高速缓冲存储器,是为了解决CPU和主存之间速度不匹配而采纳的一项重要技术

经过在主存和高速CPU之间设置一个小容量的高速存储器,在其中存放CPU常见的指令和数据,CPU对存储器的访问主要体现在对SRAM的存取,CPU能够不必加等待状态而保持高速操作

采纳CACHE技术,解决了CPU与主存之间速度不匹配的问题● 下面的描述中,( 3 ) 不是 RISC 设计应遵循的设计原则

指令条数应少一些B

寻址方式尽可能少C

采纳变长指令,功能复杂的指令长度长而简单指令长度短D

设计尽可能多的通用寄存器注释:一般原则:(1)确定指令系统时,只选择使用频度很高的指令及少量有效支持操作系统,高级 语言及其它功能的指令;(2)减少寻址方式种类,一般不超过两种;(3)让所有指令在一个机器周 期内完成;(4)扩大通用寄存器个数,一般不少于 32 个,尽量减少访存次数;(5)大多数指令用硬 联实现,少数用微程序实现;(6)优化编译程序,简单有效地支持高级语言实现

基本技术:(1)按 RISC 一般原则设计,即确定指令系统时,选最常见基本指令,附以少数对操 作系统等支持最有用的指令,使指令精简

编码规整,寻址方式种类减少到 1、2 种

(2)逻辑实现 用硬联和微程序相结合

即大多数简单指令用硬联方式实现,功能复杂的指令用