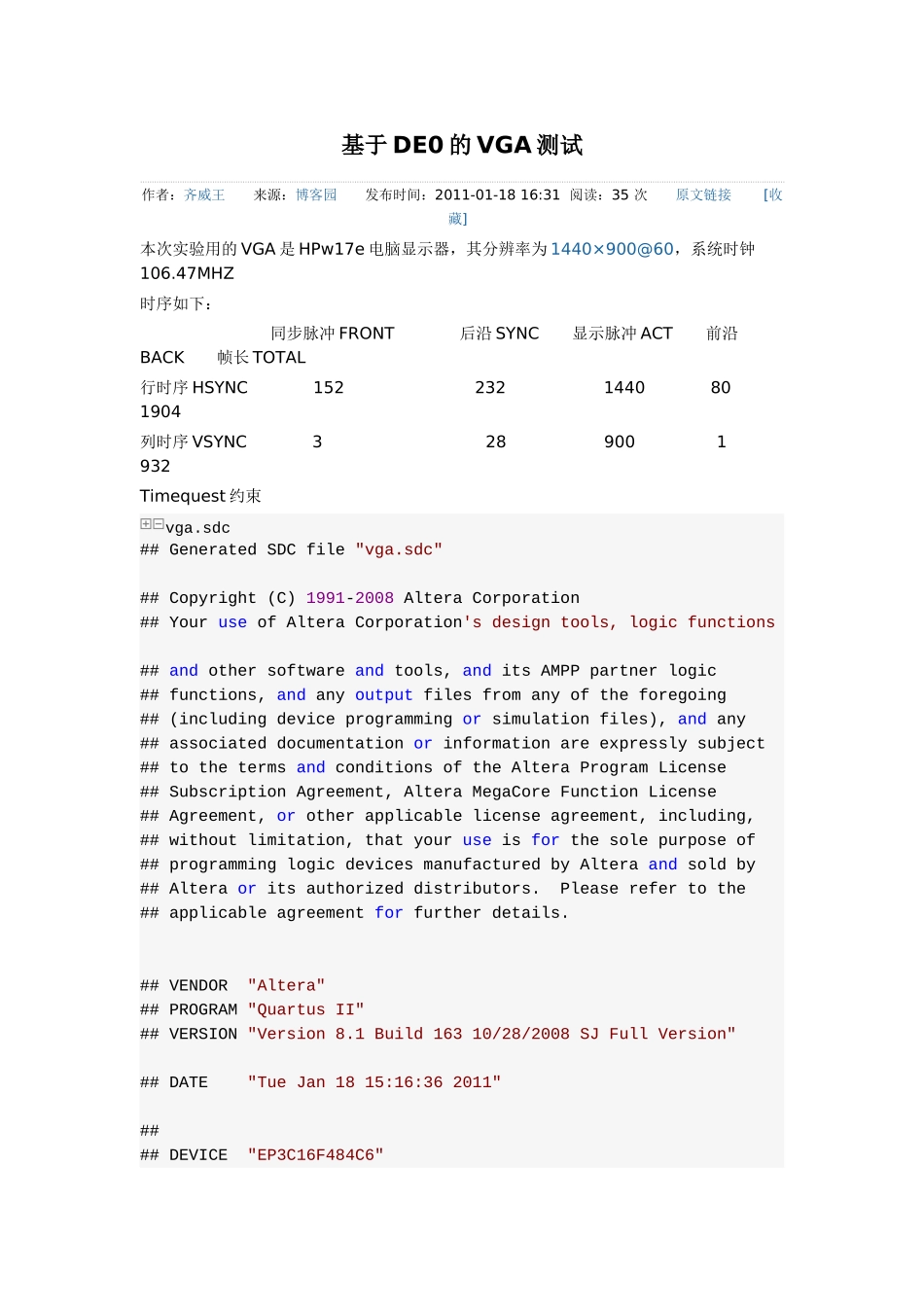

基于DE0的VGA测试作者:齐威王来源:博客园发布时间:2011-01-1816:31阅读:35次原文链接[收藏]本次实验用的VGA是HPw17e电脑显示器,其分辨率为1440×900@60,系统时钟106

47MHZ时序如下:同步脉冲FRONT后沿SYNC显示脉冲ACT前沿BACK帧长TOTAL行时序HSYNC1522321440801904列时序VSYNC3289001932Timequest约束vga

sdc##GeneratedSDCfile"vga

sdc"##Copyright(C)1991-2008AlteraCorporation##YouruseofAlteraCorporation'sdesigntools,logicfunctions##andothersoftwareandtools,anditsAMPPpartnerlogic##functions,andanyoutputfilesfromanyoftheforegoing##(includingdeviceprogrammingorsimulationfiles),andany##associateddocumentationorinformationareexpresslysubject##tothetermsandconditionsoftheAlteraProgramLicense##SubscriptionAgreement,AlteraMegaCoreFunctionLicense##Agreement,orotherapplicablelicenseagreement,including,##withoutlimitation,thatyouruseisforthesolepurposeof##programminglogicdevicesmanufacturedbyAlt