Quartus自从9

0版本以后就没有自带仿真工具

需要进行仿真要另外安装仿真工具

下面就以altera-modelsim6

6d版本介绍一个简单的VHDL语言编写的程序的仿真步骤

Quartus工具为11

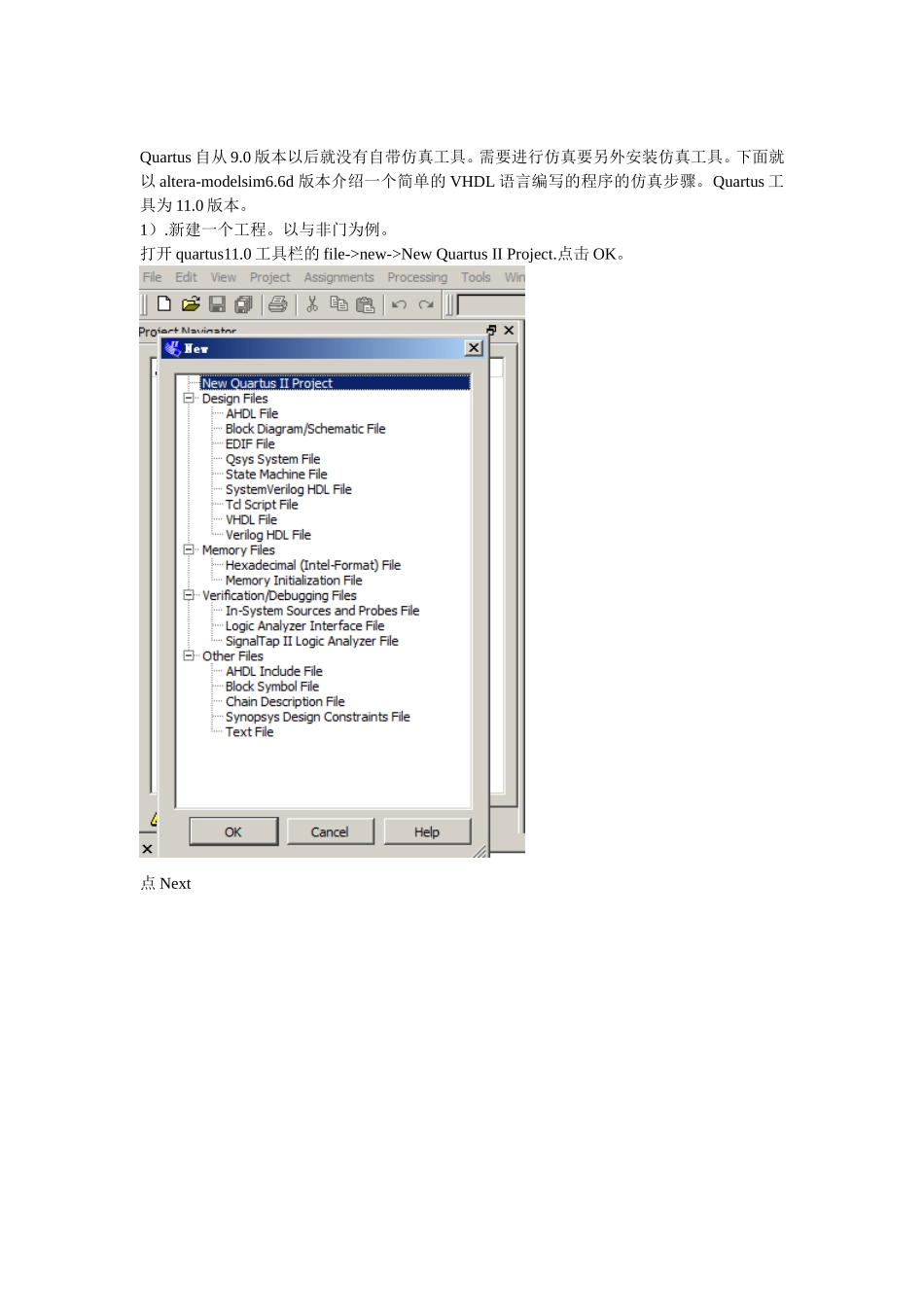

新建一个工程

以与非门为例

打开quartus11

0工具栏的file->new->NewQuartusIIProject

点Next创建工程文件夹,如andnotgate

输入工程名称

点Next先别管它,点Next选择芯片型号,因为是只是仿真,可以随便选

选择仿真工具,这里选择ModelSim-Altera

点Finish

新建了一个工程

向新建工程添加VHDL源文件File->new->VHDLFile->OK编写源程序:libraryieee;useieee

std_logic_1164

all;entityandnotgateisport(a,b:instd_logic;c:outstd_logic);endentityandnotgate;architecturert1ofandnotgateisbegincsaveas保存

编译源文件:点击Startcompilation编译成功

利用modelsim进行波形仿真要进行仿真必须先创建一个testbench的仿真激励文件

testbench文件的编写可以利用软件提供的模板进行修改

生成testbench模板processing->start->starttestbenchtemplatewriter->OK打开新生成的testbench模板

在新建工程里的simulation->modelsim里的后缀为

vht的文件

修改testbench文件,主要工作是加入要输入的信号以及输出的时间

生成的模板为LIBRARYieee;USEieee