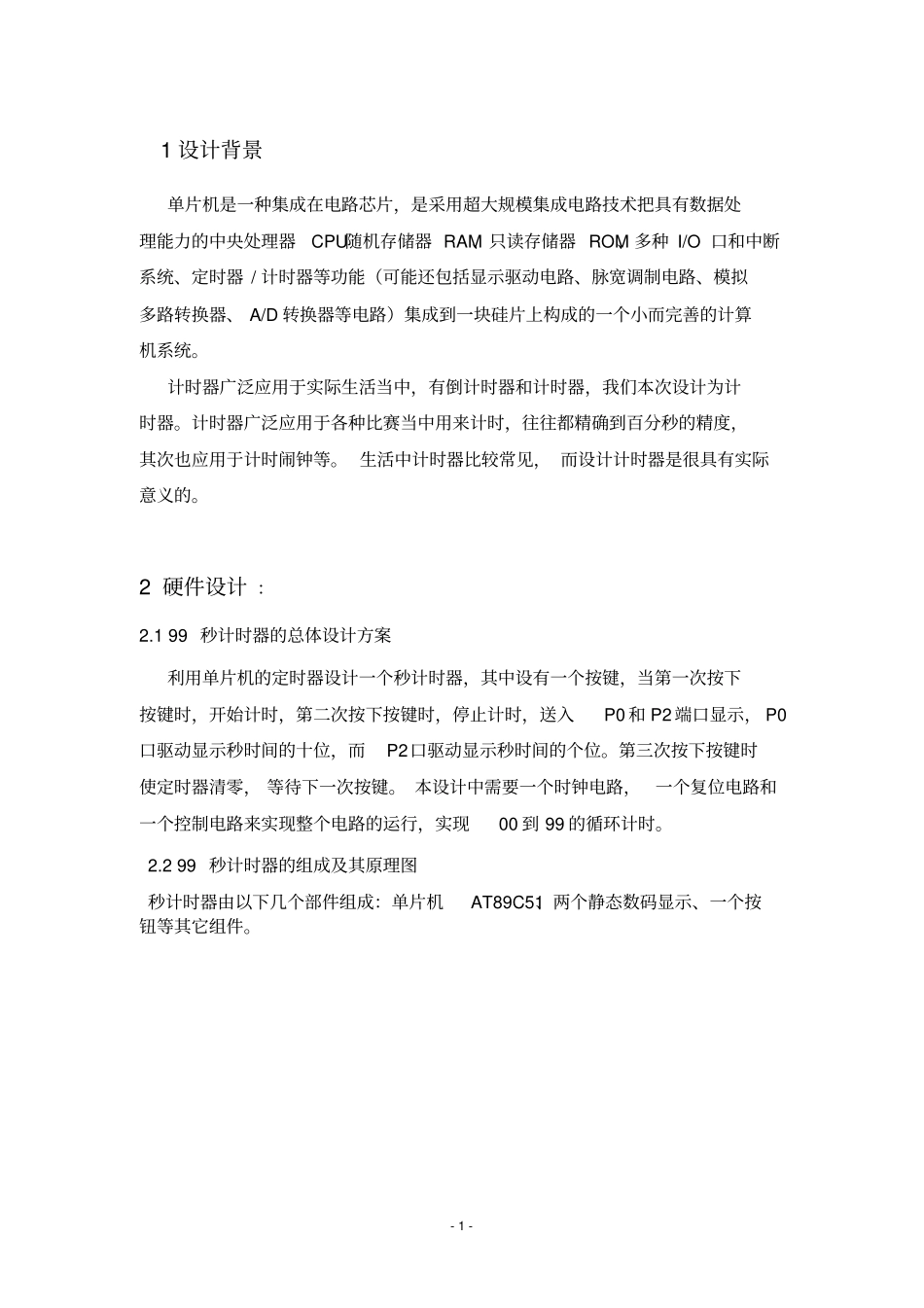

-1-1设计背景单片机是一种集成在电路芯片,是采用超大规模集成电路技术把具有数据处理能力的中央处理器CPU随机存储器RAM、只读存储器ROM、多种I/O口和中断系统、定时器/计时器等功能(可能还包括显示驱动电路、脉宽调制电路、模拟多路转换器、A/D转换器等电路)集成到一块硅片上构成的一个小而完善的计算机系统。计时器广泛应用于实际生活当中,有倒计时器和计时器,我们本次设计为计时器。计时器广泛应用于各种比赛当中用来计时,往往都精确到百分秒的精度,其次也应用于计时闹钟等。生活中计时器比较常见,而设计计时器是很具有实际意义的。2硬件设计:2.199秒计时器的总体设计方案利用单片机的定时器设计一个秒计时器,其中设有一个按键,当第一次按下按键时,开始计时,第二次按下按键时,停止计时,送入P0和P2端口显示,P0口驱动显示秒时间的十位,而P2口驱动显示秒时间的个位。第三次按下按键时使定时器清零,等待下一次按键。本设计中需要一个时钟电路,一个复位电路和一个控制电路来实现整个电路的运行,实现00到99的循环计时。2.299秒计时器的组成及其原理图秒计时器由以下几个部件组成:单片机AT89C51、两个静态数码显示、一个按钮等其它组件。-2-该电路的工作原理:AT89C51从稳压电路中获得稳定的+5V电压,接到VCC端,提供稳定的电压;P2、P0口通过电阻接到显示电路的七段数码管的abcdefg端口上,利用数码管显示数字;RST接复位电路,实现电路的复位;XTAL1、XTAL2接晶振电路;整个电路实现循环动态显示数字00~99.2.3AT89C51简单介绍及引脚说明AT89C51是一种带4K字节闪烁可编程可擦除只读存储器(FPEROM—FalshProgrammableandErasableReadOnlyMemory)的低电压,高性能CMOS8位微处理器,俗称单片机。单片机的可擦除只读存储器可以反复擦除100次。该器件采用ATMEL高密度非易失存储器制造技术制造,与工业标准的MCS-51指令集和输出管脚相兼容。AT89C51具有如下特点:40个引脚,4kBytesFlash片内程序存储器,128bytes的随机存取数据存储器(RAM),32个外部双向输入/输出(I/O)口,5个中断优先级2层中断嵌套中断,2个16位可编程定时计数器,2个全双工串行通信口,看门狗(WDT)电路,片内时钟振荡器。VCC:供电电压。GND:接地。-3-P0口:P0口为一个8位漏级开路双向I/O口,每脚可吸收8TTL门电流。当P1口的管脚第一次写1时,被定义为高阻输入。P0能够用于外部程序数据存储器,它可以被定义为数据/地址的第八位。在FIASH编程时,P0口作为原码输入口,当FIASH进行校验时,P0输出原码,此时P0外部必须被拉高。本设计中采用P0口显示计时器的十位数字。P1口:P1口是一个内部提供上拉电阻的8位双向I/O口,P1口缓冲器能接收输出4TTL门电流。P1口管脚写入1后,被内部上拉为高,可用作输入,P1口被外部下拉为低电平时,将输出电流,这是由于内部上拉的缘故。在FLASH编程和校验时,P1口作为第八位地址接收。P2口:P2口为一个内部上拉电阻的8位双向I/O口,P2口缓冲器可接收,输出4个TTL门电流,当P2口被写“1”时,其管脚被内部上拉电阻拉高,且作为输入。并因此作为输入时,P2口的管脚被外部拉低,将输出电流。这是由于内部上拉的缘故。P2口当用于外部程序存储器或16位地址外部数据存储器进行存取时,P2口输出地址的高八位。在给出地址“1”时,它利用内部上拉优势,当对外部八位地址数据存储器进行读写时,P2口输出其特殊功能寄存器的内容。P2口在FLASH编程和校验时接收高八位地址信号和控制信号。本设计中采用P2口显示计时器的个位数字。P3口:P3口管脚是8个带内部上拉电阻的双向I/O口,可接收输出4个TTL门电流。当P3口写入“1”后,它们被内部上拉为高电平,并用作输入。作为输入,由于外部下拉为低电平,P3口将输出电流(ILL)这是由于上拉的缘故。P3口也可作为AT89C51的一些特殊功能口,如下表所示:P3.0RXD(串行输入口)P3.1TXD(串行输出口)P3.2/INT0(外部中断0)P3.3/INT1(外部中断1)P3.4T0(记时器0外部输入)P3.5T1(记时器1外部输入)P3.6/WR(外部数据存储器写选通)P3.7/RD(外部数据存储器读选通)-4-P3口同时为闪烁编程和编程校验接收一些控制信号。RST:复位输入...