AT89C51单片机的特性及管脚功能AT89C51是一种带4K字节闪烁可编程可擦除只读存储器的低电压、高性能CMOS8位微处理器,俗称单片机

该器件采用ATMEL高密度非易失存储器制造技术制造,与工业标准的MCS-51指令集和输出管脚相兼容

由于将多功能8位CPU和闪烁存储器组合在单个芯片中,ATMEL的AT89C51是一种高效微控制器,为很多嵌入式控制系统提供了一种灵活性高且价廉的方案[4]

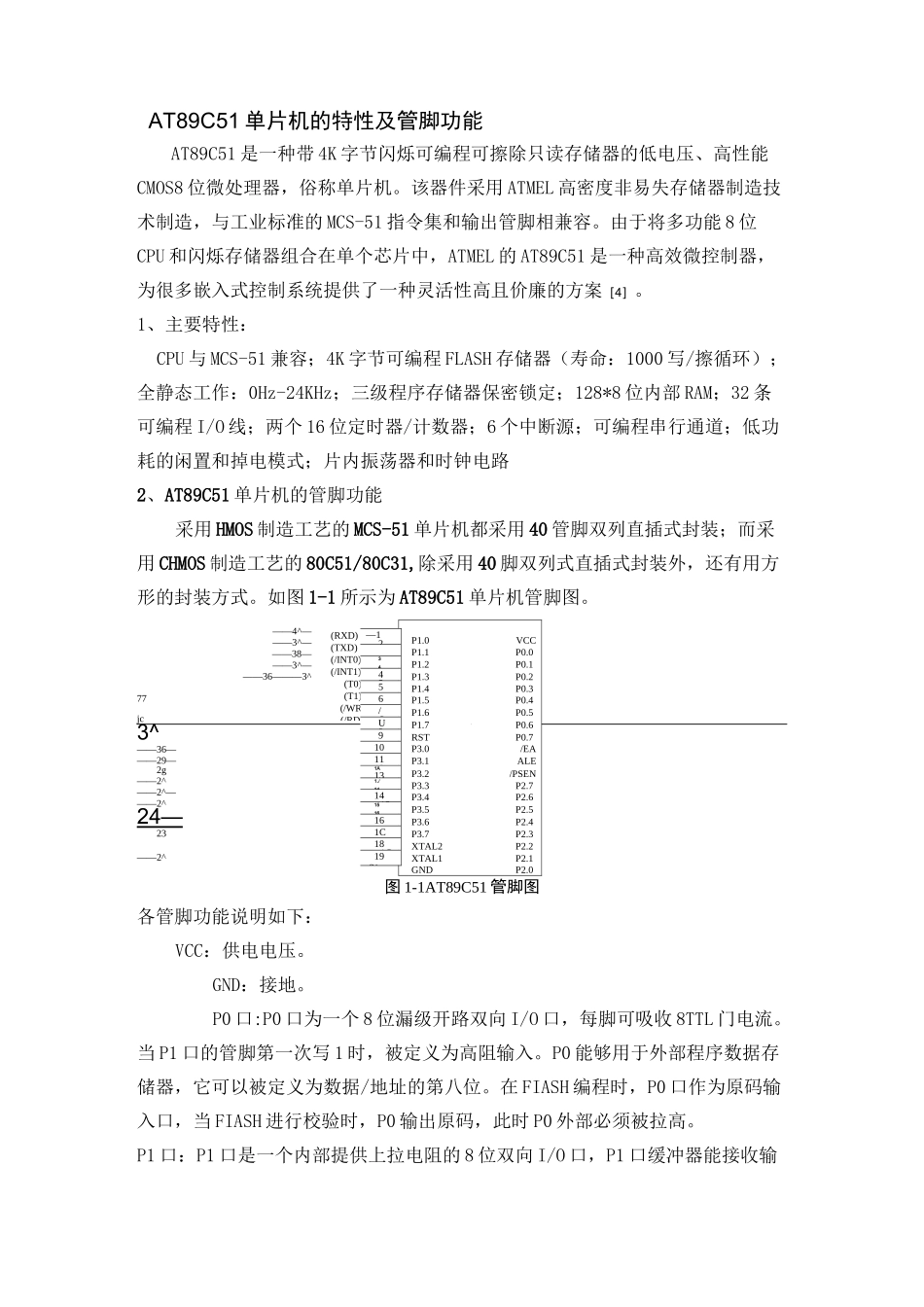

1、主要特性:CPU与MCS-51兼容;4K字节可编程FLASH存储器(寿命:1000写/擦循环);全静态工作:0Hz-24KHz;三级程序存储器保密锁定;128*8位内部RAM;32条可编程I/O线;两个16位定时器/计数器;6个中断源;可编程串行通道;低功耗的闲置和掉电模式;片内振荡器和时钟电路2、AT89C51单片机的管脚功能采用HMOS制造工艺的MCS-51单片机都采用40管脚双列直插式封装;而采用CHMOS制造工艺的80C51/80C31,除采用40脚双列式直插式封装外,还有用方形的封装方式

如图1-1所示为AT89C51单片机管脚图

——4^———3^———38———3^———36———3^77jc3^——36———29—2g——2^——2^———2^24—23——2^图1-1AT89C51管脚图各管脚功能说明如下:VCC:供电电压

GND:接地

P0口:P0口为一个8位漏级开路双向I/O口,每脚可吸收8TTL门电流

当P1口的管脚第一次写1时,被定义为高阻输入

P0能够用于外部程序数据存储器,它可以被定义为数据/地址的第八位

在FIASH编程时,P0口作为原码输入口,当FIASH进行校验时,P0输出原码,此时P0外部必须被拉高

P1口:P1口是一个内部提供上拉电阻的8位双向I/O口,P1口缓冲器能接收输(RXD)(TXD)(/INT0)(/INT1)(T0)(T1)(/