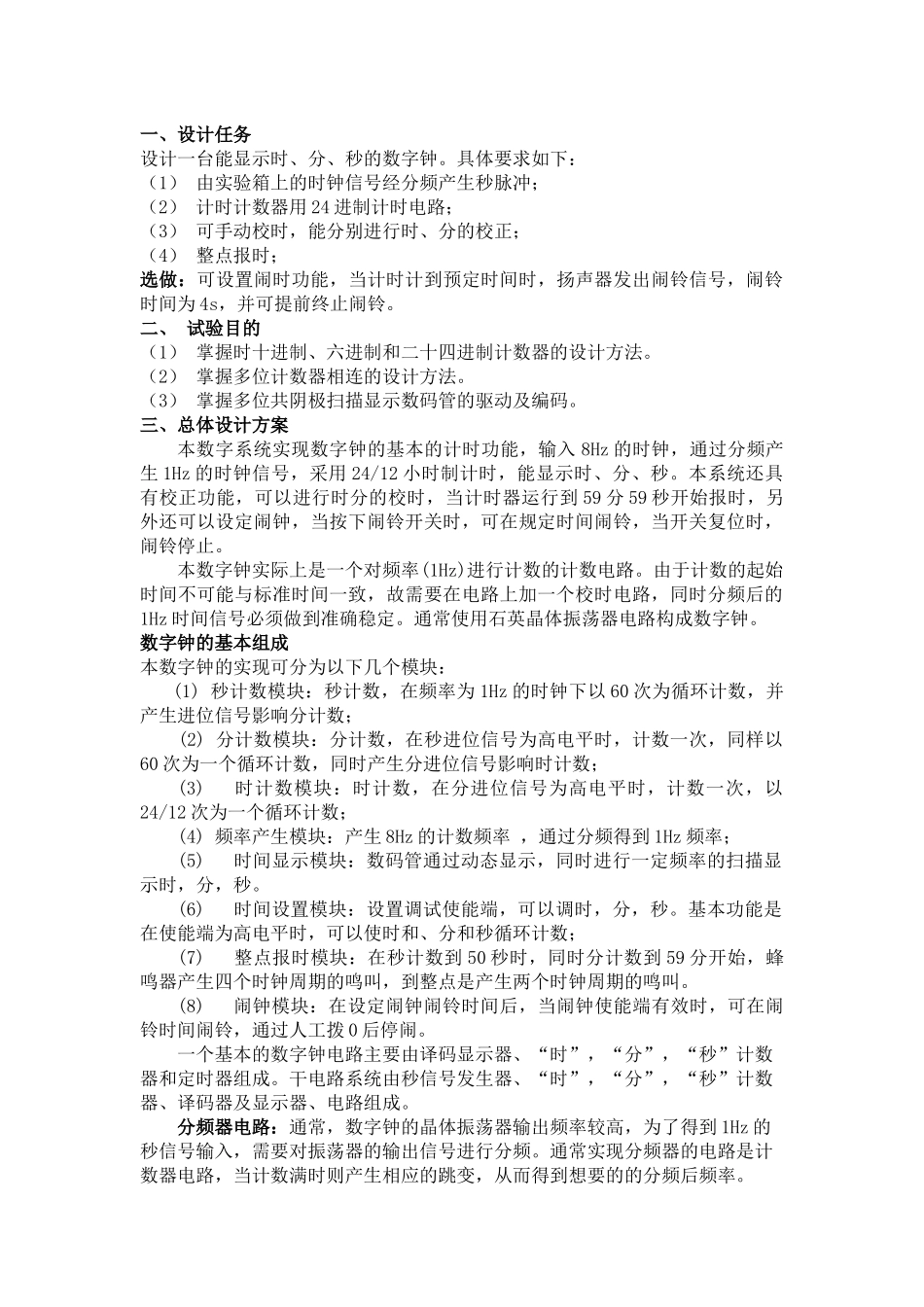

EDA 课程设计报告 ——数字钟设计班 级:学 号:姓 名:一、设计任务设计一台能显示时、分、秒的数字钟。具体要求如下:(1) 由实验箱上的时钟信号经分频产生秒脉冲;(2) 计时计数器用 24 进制计时电路;(3) 可手动校时,能分别进行时、分的校正;(4) 整点报时;选做:可设置闹时功能,当计时计到预定时间时,扬声器发出闹铃信号,闹铃时间为 4s,并可提前终止闹铃。二、 试验目的(1) 掌握时十进制、六进制和二十四进制计数器的设计方法。(2) 掌握多位计数器相连的设计方法。(3) 掌握多位共阴极扫描显示数码管的驱动及编码。三、总体设计方案本数字系统实现数字钟的基本的计时功能,输入 8Hz 的时钟,通过分频产生 1Hz 的时钟信号,采用 24/12 小时制计时,能显示时、分、秒。本系统还具有校正功能,可以进行时分的校时,当计时器运行到 59 分 59 秒开始报时,另外还可以设定闹钟,当按下闹铃开关时,可在规定时间闹铃,当开关复位时,闹铃停止。本数字钟实际上是一个对频率(1Hz)进行计数的计数电路。由于计数的起始时间不可能与标准时间一致,故需要在电路上加一个校时电路,同时分频后的1Hz 时间信号必须做到准确稳定。通常使用石英晶体振荡器电路构成数字钟。数字钟的基本组成本数字钟的实现可分为以下几个模块:(1) 秒计数模块:秒计数,在频率为 1Hz 的时钟下以 60 次为循环计数,并产生进位信号影响分计数; (2) 分计数模块:分计数,在秒进位信号为高电平时,计数一次,同样以60 次为一个循环计数,同时产生分进位信号影响时计数;(3) 时计数模块:时计数,在分进位信号为高电平时,计数一次,以24/12 次为一个循环计数;(4) 频率产生模块:产生 8Hz 的计数频率 ,通过分频得到 1Hz 频率;(5) 时间显示模块:数码管通过动态显示,同时进行一定频率的扫描显示时,分,秒。(6) 时间设置模块:设置调试使能端,可以调时,分,秒。基本功能是在使能端为高电平时,可以使时和、分和秒循环计数;(7) 整点报时模块:在秒计数到 50 秒时,同时分计数到 59 分开始,蜂鸣器产生四个时钟周期的鸣叫,到整点是产生两个时钟周期的鸣叫。(8) 闹钟模块:在设定闹钟闹铃时间后,当闹钟使能端有效时,可在闹铃时间闹铃,通过人工拨 0 后停闹。一个基本的数字钟电路主要由译码显示器、“时”,“分”,“秒”计数器和定时器组成。干电路系统由秒信号发生器、“...