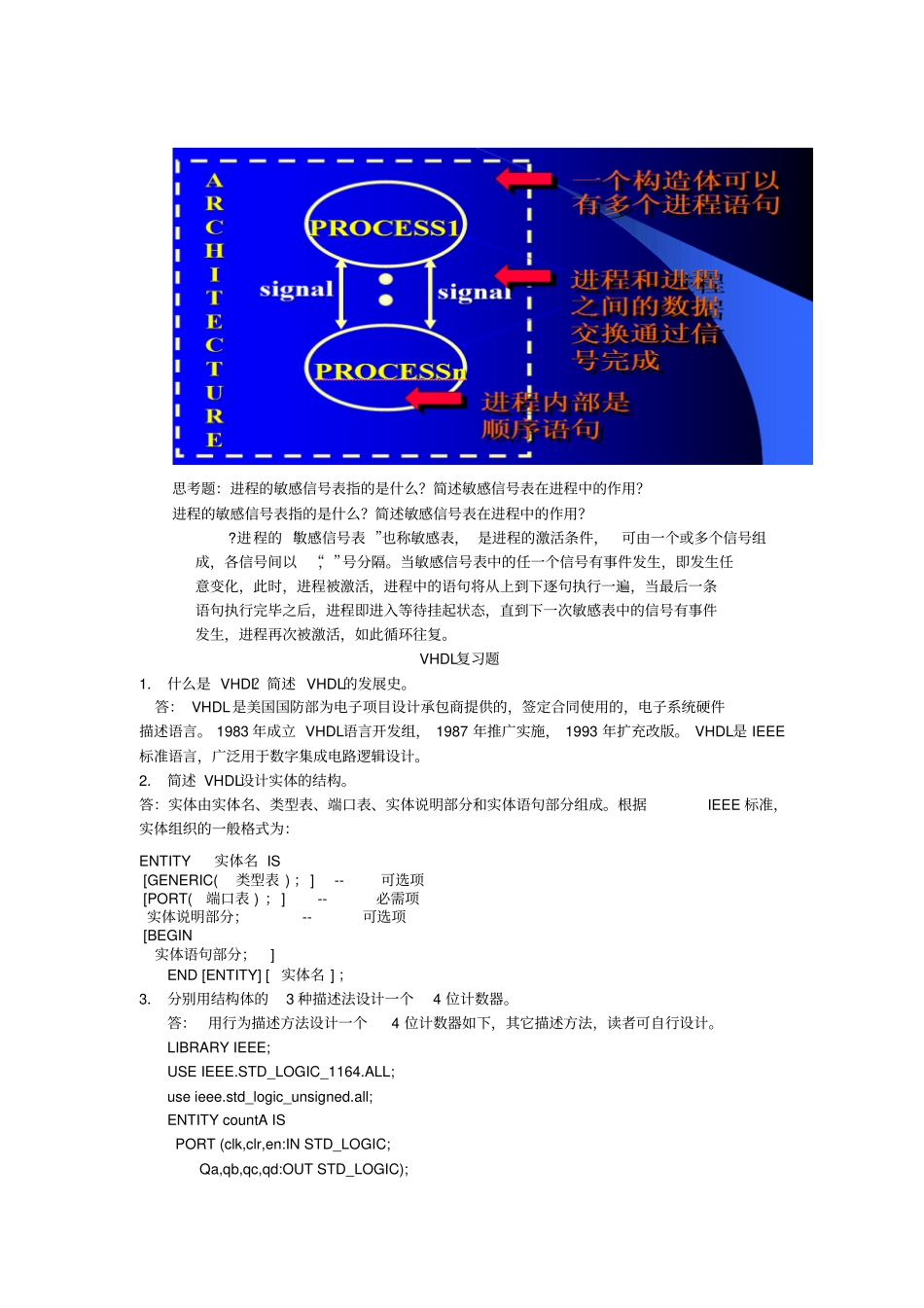

思考题:进程的敏感信号表指的是什么?简述敏感信号表在进程中的作用?进程的敏感信号表指的是什么?简述敏感信号表在进程中的作用??进程的 “敏感信号表 ”也称敏感表, 是进程的激活条件,可由一个或多个信号组成,各信号间以“,”号分隔。当敏感信号表中的任一个信号有事件发生,即发生任意变化,此时,进程被激活,进程中的语句将从上到下逐句执行一遍,当最后一条语句执行完毕之后,进程即进入等待挂起状态,直到下一次敏感表中的信号有事件发生,进程再次被激活,如此循环往复。VHDL复习题1. 什么是 VHDL?简述 VHDL的发展史。答: VHDL是美国国防部为电子项目设计承包商提供的,签定合同使用的,电子系统硬件描述语言。 1983 年成立 VHDL语言开发组, 1987 年推广实施, 1993 年扩充改版。 VHDL是 IEEE标准语言,广泛用于数字集成电路逻辑设计。2. 简述 VHDL设计实体的结构。答:实体由实体名、类型表、端口表、实体说明部分和实体语句部分组成。根据IEEE 标准,实体组织的一般格式为:ENTITY 实体名 IS [GENERIC(类型表 ) ;] --可选项 [PORT(端口表 ) ;] --必需项实体说明部分; --可选项 [BEGIN 实体语句部分;] END [ENTITY] [实体名 ] ;3. 分别用结构体的3 种描述法设计一个4 位计数器。答: 用行为描述方法设计一个4 位计数器如下,其它描述方法,读者可自行设计。LIBRARY IEEE; USE IEEE.STD_LOGIC_1164.ALL; use ieee.std_logic_unsigned.all; ENTITY countA IS PORT (clk,clr,en:IN STD_LOGIC; Qa,qb,qc,qd:OUT STD_LOGIC); END countA; ARCHITECTURE example OF countA IS SIGNAL count_4:STD_LOGIC_vector (3 DOWNTO 0); BEGIN Qa <= count_4(0); Qb <= count_4(1); Qc <= count_4(2); Qd <= count_4(3); PROCESS (clk,clr) BEGIN IF (clr = '1' ) THEN Count_4 <= "0000"; ELSIF (clk'EVENT AND clk = '1' ) THEN IF (en = '1' ) THEN IF (count_4 = "1111") THEN count_4 <= "0000"; ELSE count_4 <= count_4+ '1'; END IF; END IF; END IF; END PROCESS; END example; 1. 什么叫对象?对象有哪几个类型?答:在 VHDL语言中,凡是可以赋于一个值的客体叫对象(object)。VHDL对象包含有专门数据类型,主要有4 个基本类型:常量(CONSTANT)、信号 (SIGNAL) 、变量 (VARIABLE)...