时序约束 当 程 序 编 译 出 现 时 序 问 题 , 并 且 影 响 具 体 功 能 实 现 时 采 取 更 强 的 时 序 约 束 , 如 下图 所 示 : 具 体 解 决 方 式 是 进 行 时 序 约 束 , 以 调 整 时 序

具 体 操作步骤如 下 : 1

右击 TimeQuest Timing Analyzer 选择 open

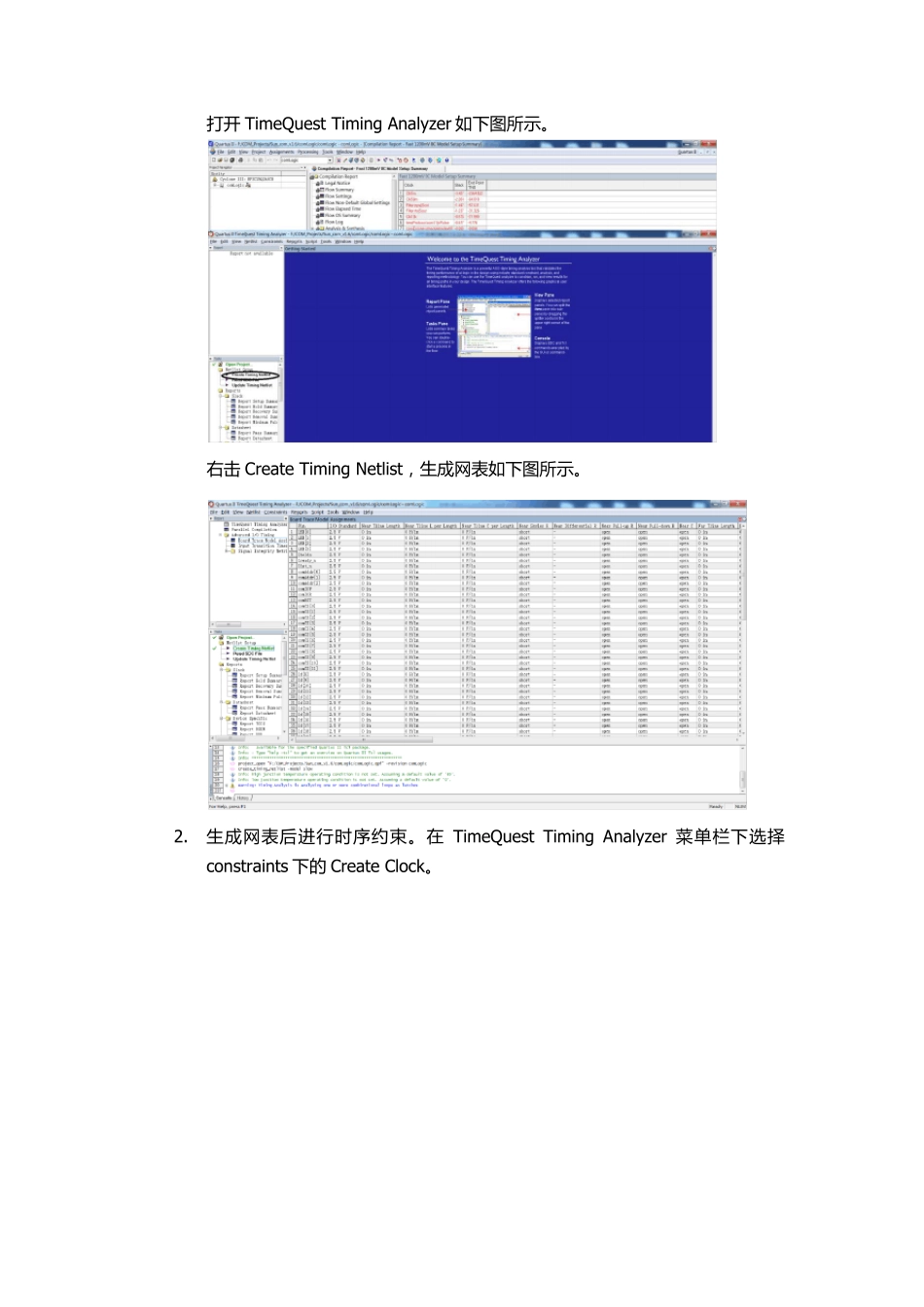

打 开 TimeQuest Timing Analyzer 如 下 图 所 示

右击 Create Timing Netlist,生成网表如 下 图 所 示

生成网表后进行时序约束

在 TimeQuest Timing Analyzer 菜单栏下 选择constraints 下 的 Create Clock

依 次 进 行 时 钟 设 置 , Targets 需 要 进 行 选 择

设 置 完毕如下图, 点击 Run 设 置完毕

在次 选 择TimeQuest Timing Analyzer 菜单栏下选 择constraints 下的 Create Generated Clock, 对约束时 钟 进 行 设 置

设 置 完毕点击 Run

运 行 完 毕 后 右 击Write SDC File 选 择Start , 如 下 图 将 文 件 保 存 为comLogic

sdc 的文 件

将3 步骤中产生的文 件 加入工程, 重新编译

编译结果如 下 图 , 可以看到红色文 字全部消失

则时序约束完 成

但 是 在 实 际 应 用 过 程 中 此 时 有 可 能 在Fast 1200mV 0C Model 的 Hold Summary 仍 然 出 现 问 题 ( 本 次 结 果 没 有 出 现 问 题 ) 如 下 图 所 示 : 此 时 需 要 将 主 菜 单 下